**Computer Engineering**

工程应用技术与实现。

文章编号: 1000-3428(2006)21-0255-03

文献标识码: A

中图分类号: TP302

# 基于 Q-Coder 算术编码器的 IP 核设计

毛文娟,王建立,张孝三

(上海工程技术大学高职学院,上海 200437)

摘 要:设计了一种实现算术编码的集成电路 IP 核,可用于下一代静止图像压缩标准 JPEG2000 编码系统中。采取易于硬件实现的二进制算术编码算法,分析了该 IP 核的各个模块和时序,在 ModelSim 软件中进行了功能仿真,在 Quartus 软件中完成了综合以及布局布线,并在自行设计的一块 FPGA 的 PCI 开发板上进行了验证和性能分析。实验结果表明,对相同的图像进行编码,该 IP 核的处理时间仅为软件处理时间的 41%。该文的研究对于 JPEG2000 在实际中的应用有着重要的意义。

**关键词:**算术编码;现场可编程门阵列;大概率符号;小概率符号

# IP Core Design Based on Q-Coder Arithmetic Coding Algorithm

MAO Wenjuan, WANG Jianli, ZHANG Xiaosan

(Vocational Technical College, Shanghai University of Engineering Science, Shanghai 200437)

[Abstract] An circuit IP performing arithmetic coding is designed to be implemented in JPEG2000, which is the newly developed still image processing standard. A binary arithmetic coding algorithm, which is easy to be implemented in hardware is used. The module structure and time sequence of the IP core are described. Function verification is carried out with Model-sim, synthesis and routing are conducted with Quartus II. The design is verified on a PCI-based FPGA development board. With the same inputs, the outputs show that the hardware arithmetic encoder designed by this paper can perform its computation in approximately 40% of the time taken by the arithmetic coding module in the Jasper software. The research of the thesis makes it possible for JPEG2000 to be used in reality.

**Key words** Arithmetic coding; FPGA; More probable symbol (MPS); Less probable symbol (LPS)

# 1 概述

JPEG2000<sup>[1,2]</sup>是新的静止图像压缩标准,它具有的多种特性使得它有着广泛的应用前景。目前为止,JPEG2000 的解决方案比较少,并且其中的绝大部分是软件解决方案:Jasper<sup>[3]</sup>软件是经IEC JTC1/SC29/WG1 小组推荐使用的实现JPEG2000 的为数不多的软件之一。

由于软件实现 JPEG2000 的时间开销比较大,因此, JPEG2000 编码系统很难应用于实际系统中;硬件解决方案由于处理速度大大提高,因而用硬件实现 JPEG2000 具有广泛的市场前景。但是,JPEG2000 算法复杂,完全用硬件实现比较困难;然而使用硬件实现 JPEG2000 中的某些模块,相对而言就比较容易实现,同时也能大大提高编码效率。

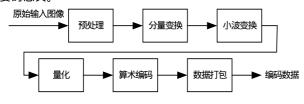

图 1 为 JPEG2000 的几个基本模块。文献[4]指出,软件处理中,图 1 中的算术编码模块的时间开销占据了整个软件时间开销的 40%左右,若使用硬件实现算术编码模块必然能大大提高编码速度,对于提高 JPEG2000 的编码速度有着重要的意义。

图 1 JPEG2000 基本模块

# 2 O-coder 算术编码器原理

Q-coder算术编码是一种特殊的高效自适应二进制算术

编码器。其输入是成对待编码数据D(DATA)以及上下文CX(CONTEXT),数据D和上下文CX是由比特平台(bit plane)<sup>[1]</sup>产生的;输出则是压缩数据CD(COMPRESSED DATA)。在JPEG2000中,上下文指D周围8个相邻比特的状态,这些状态被特定的规则划分为19类,称为19种上下文。每种上下文都包含两部分内容,一部分选择了对数据D编码时使用的概率估计值对应的索引,另一部分决定了当前大概率符号所代表的符号,这两部分内容将在编码后被更新。

# 2.1 区间的递归划分

概率区间的递归划分是二进制算术编码的基础。每执行 一次二元判定,当前概率区间就被划分成为两个子区间,并 在必要的时候修改输出码流,使之指向该符号所在的概率子 区间的下界。

在区间划分时,小概率符号的子区间和大概率符号的子区间这样排序:通常取靠近0的区间作为 MPS 的子区间,因此,若编码的是 MPS,则应向输出码流中加入 LPS 子区间的长度。这种约定要求把编码的符号区别为 LPS 或 MPS,而不是0或者1。因此在对一次二元判定编码时,必须知道该判定的 LPS 子区间的长度和 MPS 的含义。

#### 2.2 编码约定和近似计算

Q-coder 算术编码器设置两个寄存器:一个是概率区间宽度寄存器 A,用于存放子区间的宽度,另一个是码字寄存器

基金项目:上海工程技术大学青年科学基金资助项目(2004Q17) 作者简介:毛文娟(1977 - ),女,助教,主研方向:图像处理的硬件

实现;王建立,副教授;张孝三,高级讲师

**收稿日期:** 2006-01-29 **E-mail:** wenjuanmao@hotmail.com

C,用来表示概率区间的下限。编码过程使用固定精度的整数运算和小数的整型表示形式,即 X'8000'代表十进制小数 0.75。概率区间 A 的范围是  $0.75 \le A < 1.5$ ,并且当 A 的整型值小于 X'8000'时,把 A 翻倍,即把 A 限制在十进制范围 0.75-1.5 之间,这个"翻倍"过程称为重整化。当 A 进行重整化时,C 也必须同时翻倍。为了防止寄存器 C 发生上溢,每隔一段时间,应将寄存器 C 的高位部分移出并送至另外的寄存器中。

将 A 限制在十进制范围  $0.75 \sim 1.5$  之间,概率区间的划分可以使用简单的算术近似方法。如果 LPS 当前的概率估计值是  $Q_a$ ,则子区间的精确计算如下进行:

$Q_a * A = LPS$ 概率子区间

A-(Q\*A)=MPS概率子区间

由于 A 的十进制值近似于 1, 因此可用下式作近似计算:

$Q_s = LPS$ 概率子区间

$A-Q_a=MPS$ 概率子区间

如果输入符号为 MPS,那么编码器进行如下运算:

$C \leftarrow C + Q_{\circ}$

$A \leftarrow A - Q_e$

若输入符号为 LPS,则 C 保持不变,  $Q_e \rightarrow A$ ,必要的时候需对 A、C 进行重整化。

# 3 算术编码器的实现

#### 3.1 算术编码流程

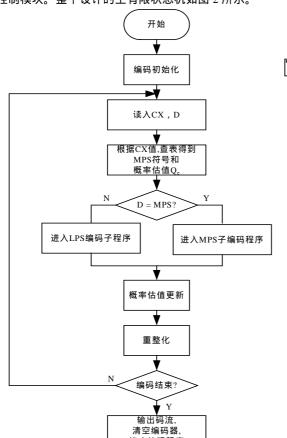

所有的设计都是用Verilog硬件描述语言编写的,由上述描述可知,算术编码器的输出不仅和当前状态有关,而且和输入也相关,所以本文选择Mearly有限状态机<sup>[5]</sup>来描述复杂的控制模块。整个设计的主有限状态机如图 2 所示。

图 2 算术编码主有限状态机

#### 3.2 模块设计

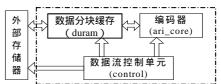

duram 是双口 sram 作为片内存储单元存储输入的数据,当采用 FPGA 进行验证时,直接调用 Altera 公司的宏功能块即可;ari\_core 是实现算术编码的运算处理单元,包含一个存储概率估值和当前 MPS 符号的表以及 LPS 和 MPS 编码子程序;模块 control 是数据流控制单元,用于组织片内存储单元duram 和运算处理单元 ari\_core 以及片外 sram 的数据交换。模块 control 是整个设计的控制单元,负责调度以上各个模块,产生控制和联络信号以及地址信号。模块结构原理如图3 所示。

图 3 模块结构原理

#### 3.3 电路验证

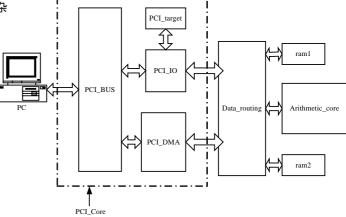

将布局布线后生成的文件下载到自行设计的一块FPGA的PCI开发板里进行验证,如图 4 所示。板上是一片Alteracyclone系列FPGA ep1c12qfp240,该FPGA含有约 25 万逻辑门、30KB内部RAM。PCI接口控制逻辑也是在FPGA中实现 [6-8],然后编写PCI驱动程序和应用程序,先由Jasper软件处理,抽取软件中量化模块处理后的数据,输入FPGA中进行处理,再将数据返回给软件中的下一模块,验证本文设计的算术编码IP核的正确性,并计算处理时间。

图 4 算术编码硬件电路的 PCI 验证系统

#### 4 实验结果与分析

(1)将 Verilog 源程序在 Quartus 软件中综合后,得到的参数如下:

1)器件名称: EP20K200efc484-2x:

2)FPGA 时钟最高频率: 45.18MHz;

3)Total logic elements: 3660/8320 (44%).

(2)功能验证。目前,只有JBIG<sup>[8]</sup>标准中有验证算术编码器编码正确性的测试向量,因此该测试向量被用以测试本文设计IP核的正确性。需要说明的是:JBIG标准中的算术编码器会产生"FF AC"标志位<sup>[8]</sup>,而JPEG2000 中的MQ-Coder算术编码器并不产生该标志位<sup>[1]</sup>。

将 JBIG 中的测试向量作为输入,经过本文设计的算术编码 IP 核处理后的结果如图 5 所示,由图 5 可知本文设计的算术编码 IP 核完全正确。

| Name           | Value Value                                              | Stimulator | 112,22   112,24 |

|----------------|----------------------------------------------------------|------------|-----------------|

| ⊞ № byteOutReg | DF                                                       |            |                 |

| ™ encReady     | 1                                                        |            |                 |

| л byteReady    | 0                                                        |            |                 |

| ⊞ nr cRegOut   | 0007FE00                                                 |            |                 |

| ⊞ ™ aRegOut    | 00008401                                                 |            |                 |

| ⊞ r ctRegOut   | 08                                                       |            |                 |

| ™ mpsRegOut    | 1                                                        |            |                 |

| ⊞ ″indexRegOut | 12                                                       |            |                 |

| ₁r END_SIM     | true                                                     |            | Xtrue X         |

| ⊞ r inCount    | 0000                                                     |            |                 |

| ⊞ ™ outCount   | 001C                                                     |            | X001C           |

| ⊞ ™ dataInReg  | 000000000000000000000000000000000000000                  |            |                 |

| ⊞ ™ dataOutReg | 84C73BFCE1A1430402200000410DBB86F4317FFF88FF37471ADB6ADF |            | X               |

图 5 JBIG 测试向量输出结果

(3)由概述可知,Jasper 软件具有一定的权威性,因此在实验中被使用。表 1 列出了对于同一个图像文件,Jasper 软件中算术编码模块执行所需的时间和本文设计的算术编码 IP 核执行所需的时间以及两者时间之比。

表 1 算术编码执行时间比较

| 图像大小        | 压缩   | Japer 执行 | FPGA 核执 | 软、硬件执  |  |  |  |

|-------------|------|----------|---------|--------|--|--|--|

| (Lena)      | 比    | 时间(ms)   | 行时间(ms) | 行时间之比  |  |  |  |

| 512*512*256 | 10:1 | 345.882  | 131.435 | 37.99% |  |  |  |

| 512*512*24b | 10:1 | 955.852  | 430.134 | 45.00% |  |  |  |

#### 5 结论

本文提出的一种实现算术编码的集成电路 IP 核,经过仿真和 FPGA 验证,能够符合 JPEG2000 标准,仿真结果表明,在相同的条件下,该 IP 核编码所需时间仅约为软件编码所需

时间的 40%,从而大大提高了算术编码的效率,使得将来其应用于实时处理系统成为可能;并且将来可以定制所需的 ASIC 电路,用于新一代数字照相机等具有广泛市场前景的 项目。

# 参考文献

- 1 Boliek M, Christopoulos C, Majani E. ISO/IEC JTC1/SC29/WG1 N1646R-2000 JPEG2000 PartI Final Committee Draft (Version 1.0)[S]. 2000.

- 2 张晓娣, 刘贵忠, 曾召华等. JPEG2000 图像压缩编码系统及其关键技术[J]. 数字电视与数字视频, 2001, (8).

- 3 Jasper Project Home Page[Z]. http://www.ece.ubc.ca/~mdadams/jasper.

- 4 Adams M D, Kossentini F. JasPer: A Software-based JPEG-2000 Codec Implementation[C]. Proc. of Int'l Conf. on Image Processing, 2000: 53-56.

- 5 陈雪松, 藤立中. VHDL 入门与应用[M]. 北京: 人民邮电出版社, 2000

- 6 陈文正, 曹 明. PCI 总线协议的 FPGA 实现及驱动设计[J]. 电子技术应用, 2003, 29(7): 15-17.

- 7 胡和平, 田宜波. 基于 FPGA 的 PCI 接口设计[J]. 计算机工程, 2003, 29(8): 156-157.

- 8 刘海平, 朱仲英. 基于 FPGA 的 PCI 总线接口设计[J]. 微型电脑应用, 2003, 19(9): 49-51.

- 9 JBIG Committee. ISO/IEC JTC 1/SC 29/WG 1 N1359-1999 14492 FCD[S]. 1999-07.

# (上接第234页)

植性,开发周期也被大大缩短,而且还能支持动态下载和升级。其次,J2ME 提供了 HTTP、TCP 等高级 Internet 协议使受限终端能以 Client/Server 方式直接访问 Internet 的信息,不同的 Client 访问不同的文件,此外还能访问本地存储区。因此要编程实现 MAIHS 中的 Agent 群体和远程认证及监控功能,J2ME 以其不菲的实力和优良的特性成为了技术首选。具体的开发技术,本文不再赘述,请参阅相关文献。

# 4 结论

本文讨论了Agent技术及其在智能家居领域中的应用,设计了一个实用性强、综合全面的MAIHS模型,具体分析了MAIHS中几种Agent的功能设计与实现机理,重点讨论了系统内Agent群体的协调策略以及身份认证机制。但该模型还有待进一步探讨和完善,如研究如何引入情境感知计算,以情境(包括计算机、人在内的整个环境)为媒介使计算设备感测情境,适应情境,提供最灵活的计算服务,提供一种人与计算机、环境的自然交互<sup>[12]</sup>,尝试着结合BDI结构和情境演算的优点<sup>[13]</sup>,构建基于情境演算的Agent,进一步提高系统的智能化将是下一步的工作重点之一。

# 参考文献

- 1 叶朝辉, 杨士元. 智能家庭网络研究综述[J]. 计算机应用研究, 2001, 18(9): 1-6.

- 2 Rutishauser U, Schaefer A, Douglas R, et al. Intelligent Buildings, A

- Multi-agent Approach[C]. Proc. of Workshop Embodied Artificial Intelligence, Zurich, Switzerland, 2002.

- 3 叶 俊, 刘贤德. 基于多主体的楼宇智能控制体系结构[J]. 计算机工程与应用, 2004, 40(19): 203-205.

- 4 韩江洪. 一种基于多 Agent 系统的智能家庭网络研究[J]. 电子科 技大学学报, 2005, 34(2): 233-235.

- 5 查先进. 信息分析与预测[M]. 武汉: 武汉大学出版社, 2005-03.

- 6 桂兵祥, 胡 晓. 智能家庭网络安全解决方案[J]. 计算机工程, 2003, 29(1): 165-167.

- 7 Jain A K, Lin Hong. Biometrics: Techniques for Personal Identification[C]. Proc. of International Symposium on Multi-spectral Image, 1998.

- 8 慧 敏. 一种改进的基于智能卡的身份鉴别方案设计[J]. 北京邮 电大学学报, 2005, 28(2): 39-41.

- 9 何致远, 胡起秀. 两级决策的开集说话人辨认方法[J]. 清华大学 学报(自然科学版), 2003, 43(4): 516-520.

- 10 王 亮, 胡卫明, 谭铁牛. 基于步态的身份识别[J]. 计算机学报, 2003, 26(3): 353-360.

- 11 王 倩, 阮海波, 李俊山. 快速模糊边缘检测算法[J]. 中国图像图形学报, 2001, 6(1): 92-95.

- 12 万亚红, 黄樟钦. 基于主动推理的情境感知系统框架[J]. 计算机 工程, 2004, 30(12): 8-9.

- 13 李 斌, 吕 建, 朱梧槚. 基于情境演算的智能体结构[J]. 软件 学报, 2003, 14(4): 733-742.