工程应用技术与实现。

No.20

文章编号: 1000-3428(2010)20-0214-03

文献标识码: A

中图分类号: TP336

# ARINC659 总线接口跨时钟的研究与设计

#### 何向栋,樊晓桠,安建峰

(西北工业大学航空微电子中心, 西安 710065)

摘 要:ARINC659 总线与机载计算机 PCI9054 接口设计中因工作时钟不同而出现亚稳态现象。为此,描述亚稳态机理,给出降低亚稳态 产生条件,提出采用同步器实现控制信号传递和格雷码+异步 FIFO 实现数据传输。结合 PCI9054 接口信号时序,设计总线接口模块,通过 Verilog 编码实现进行仿真实验。结果表明,异步 FIFO 解决了 ARINC659 与 PCI9054 之间的跨时钟数据传输。

关键词:ARINC659 总线;跨时钟;亚稳态;异步FIFO

# Study and Design of ARINC659 Bus Interface Cross-clock

HE Xiang-dong, FAN Xiao-ya, AN Jian-feng

(Aviation Microelectronics Center, Northwestern Polytechnical University, Xi'an 710065, China)

[Abstract] Metastability emerges from designing the interface between ARINC659 and PCI9054 because of the two different clocks. This paper describes the mechanism of the metastability, gives conditions for reducing metastable produce, and proposes achieving control signal transmission by synchronizer and data transfer by Gray code + FIFO. With PCI9054 interface signal timing, the paper designs the bus interface module, and implements the interface design with the Verilog language. Result shows that asynchronization FIFO solves cross-clock data transfer between ARINC659 and PCI9054.

[Key words] ARINC 659 bus; cross-clock; metastability; asynchronization FIFO

## 概述

ARINC659 总线[1-2]协议是美国航空无线电协会制定,由 Honeywell 公司研制并成功应用于波音 777 飞机信息管理系 统(AIMS)的数据总线,是航空电子数字数据传输标准。 ARINC659 工作在 60 MHz, 机载 PCI9054 工作在 33 MHz, 数据跨时钟传输,出现亚稳态。本文通过同步器和异步 FIFO 实现 2 种总线的跨时钟接口设计,以 Verilog 编码实现,仿真 和 FPGA 下载实现结果表明设计是正确的。

# 2 ARINC659 总线协议及接口功能分析

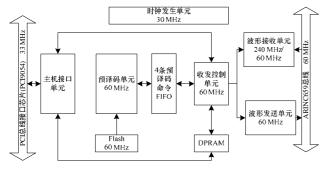

ARINC659 总线采用表驱动均衡访问(TDPA)的通信机 制,其操作按照预定的时间命令表进行,用于在线可更换模 块(LRM)之间的数字数据传送。ARINC659 总线接口芯片系 统模块如图 1 所示。

图 1 ARINC 659 总线接口芯片模块

主机接口单元是本文的重点,其主要功能有以下2点: (1)主机读取 ARINC659 总线接口芯片内部寄存器并完成设 置;(2)支持主机通过 PCI9054 芯片读写 ARINC659 总线系统

中 DPRAM 内容及其 4 种总线周期:单步 32 位读写,连续 32 位读写。

ARINC659 总线接口芯片内部工作时序为 60 MHz, PCI 总线接口芯片 PCI9054 工作时序为 33 MHz, 机载计算机与 ARINC659 总线芯片的跨时钟数据收发,导致亚稳态发生, 系统稳定性下降。设计中 ARINC659 总线接口芯片不仅要正 确接收 PCI9054 芯片 LHOLD、LW/R、READY 和 WAIT 等 控制信号,还要正确接收地址线 LA 等并行总线信息。控制 信号与并行总线信号的跨时钟传递出现问题和解决策略不 同,下面将逐一描述。

#### 3 亚稳态

ARINC659 与 PCI9054 工作于不同的时钟域下,直接在 触发器的时钟上升沿对数据采集,由于时序不稳定导致采集 错误,出现亚稳态现象。亚稳态的发生是时序不满足输入端 建立时间/保持时间的要求,而导致输出端信号不确定,造成 逻辑判断出错。数据突变和时钟边沿的接近程度决定了亚稳 态故障的产生。为降低跨时钟数据亚稳态的产生,应满足下 面 2 个条件公式。

(1)避免违反建立时间:

$$t_{\text{logic-max}} < T_{\text{clock}} - t_{\text{clock}-Q_{\text{max}}} - t_{\text{skew}} - t_{\text{set-up}}$$

(1)

(2)避免违反保持时间:

$$t_{\log \text{ic-min}} > t_{\text{hold}} + t_{\text{skew}} - t_{\text{clock-}Q_{\text{min}}}$$

(2)

作者简介:何向栋(1984-),男,硕士研究生,主研方向:计算机系 统结构; 樊晓桠, 教授、博士生导师; 安建峰, 讲师、博士 **收稿日期:**2010-02-20 E-mail: nwpuxiangdong@gmail.com

其中, $t_{\text{clock-}}Q_{\text{max}}$ 是时钟沿变化到数据输出端变化(最慢情况); $t_{\text{clock-}}Q_{\text{min}}$  是时钟沿变化到数据输出端变化(最快情况); $t_{\text{skew}}$ 表示时间的偏移量。

## 4 主机接口单元设计

#### 4.1 控制信号的同步器设计

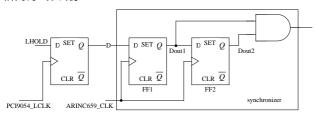

PCI9054 信号 LHOLD 跨时钟传入 ARINC659 芯片时, 经过同步器同步后才能被正确接收,降低亚稳态发生的概率。同步器通过保证信号的建立和保持时间,减少亚稳态发生。

主机接口单元采用图 2 所示同步器结构实现 LHOLD 控制信号的传递。其他控制信号 LW/R、READY 和 WAIT 等以相同方式实现。

图 2 LHOLD 信号同步器跨时钟传递设计实现

图 2 采用 2 个触发器的串联,添加一个与门构建同步器。信号LHOLD从 PCI9054\_LCLK 时钟进入 ARINC659\_CLK 时钟,经过了两级触发器,降低单个触发器出现的亚稳态概率。当 LHOLD 信号变化和 ARINC659\_CLK 上边沿非常接近时,出现亚稳态,但经过 FF1 的锁存和 ARINC659\_CLK 一个周期信息保持,基本能够把不稳定的信号修正,从而在ARINC659\_CLK 的下一个时钟沿,FF2 正确采集到 Doutl。如果 FF1 出现的亚稳态较严重,在下一个 ARINC659\_CLK 时钟沿还未消除,致使 FF2 也进入亚稳态。校验电路与门较好地解决了后一种情况发生概率,保证信号正确进入ARINC659 芯片内部。值得一提的是,两级同步器出现亚稳态的概率是单个触发器的平方,显著提高系统的可靠性。但对于总线型信号 LA 不适用,原因在于:LA 数据各位变化不同并且同步器性能也不可能完全相同,数据到达 ARINC659总线芯片内部参差不齐,亚稳态出现几率大大增加。

#### 4.2 数据传输的异步 FIFO 设计

异步  $FIFO^{[3]}$ 由同步器、比较器和  $DPRAM(双端口\ RAM)$  等构成,它解决了 ARINC659 和 PCI9054 之间地址与数据的速度匹配问题,并且支持主机接口实现 PCI9054 芯片 4 种总线周期。

#### 4.2.1 Gray 码和地址比较器设计

ARINC659 和 PCI9054 地址是顺序增加的。对二进制地址增一位,地址总线变化不只一位,地址跨时钟同步增加亚稳态发生概率。由于相邻 Gray 码<sup>[4]</sup>变化,只相差一位,解决地址总线各位通过不同性能同步器时的竞争,非常适合地址总线同步,但 Gray 码不适合比较。设计中对 DPRAM 的读写和比较采用地址二进制,同步使用 Gray 码。

### 二进制转换 Gray 码如下:

$G_{N}\!\!=\!\!B_{N};\;\;G_{N-1}\!\!=\!\!B_{N}\!\!+\!B_{N-1};\;\;G_{N-2}\!\!=\!\!B_{N-1}\!\!+\!B_{N-2}...G_{1}\!\!=\!\!B_{2}\!\!+\!B_{1};\;\;G_{0}\!\!=\!\!B_{1}\!\!+\!B_{0}$

Gray 码转换二进制如下:

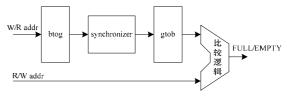

地址比较器包括 btog(二进制转换 Gray 码)、gtob(Gray 码转换二进制)、同步器和比较逻辑,如图 3 所示。比较结果

用来标识满/空标志位。

图 3 地址比较器

当遇到相同地址比较时,是写单元追到了读单元,DPRAM为满;还是读的时钟更快,DPRAM已为空,此时无法确定 DPRAM的满/空标识。解决这个问题的做法是:给读写指针增加一位高地址,在读写模块分别到达 DPRAM满时,对该位累加,这样读写地址的低 N 位地址相同而只有写模块的高地址位为"1"时,判断 DPRAM为满;读写地址完全相同时,判断 DPRAM为空。设 waddr 为写地址,raddr 为读地址,N 为地址总线位数,Verilog HDL 实现如下:

if(waddr[N-1:0] == raddr[N-1:0] &&wadrr[N]! = raddr[N])

FULL=1:

If(waddr[N:0]==raddr[N:0])

EMTPY=1;

# 4.2.2 同步延迟

设ARINC659\_CLK为写时钟,PCI9054\_LCLK为读时钟,同步器使得ARINC659 地址同步到PCI9054 至少推迟2个PCI9054\_LCLK时钟,此时ARINC659 地址已经在自己的时钟下进行累加,直接比较同步后的地址并不能反映最新地址比较情况,造成写数据错误。通过设立一个幅度参数,在它们比较时,留有一定的余地来解决问题。以空标识位为例,Verilog HDL 实现如下:

parameter INC=`b10;

if (ARINC659\_LA==PCI9054\_LA+INC)

EMPTY=1;

INC 参数避免了读写地址在各自时钟下的实际偏差,使读地址提前了 2 个地址,标识了一个"虚空"状态。这样做的目的是:通过 2 个 DPRAM 的数据寄存器的无效来保证读写操作能够正确完成。

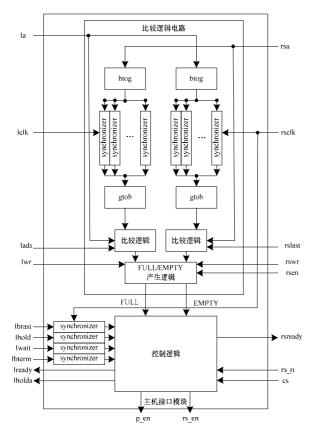

#### 4.3 主机接口单元设计

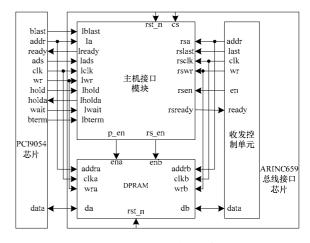

结合 4.1 节、4.2 节的设计和 PCI9054 芯片接口信号时序,实现 ARINC659 主机接口模块与内部收发控制单元、DPRAM、PCI9054 芯片连接,如图 4 所示。图 5 为主机接口模块的详细设计。

图 4 主机接口模块连接示意图

图 5 主机接口模块

(1)主机接口模块主要包含地址判断逻辑和控制逻辑,其 具体模块含有:

1)synchronizer 同步器,实现 LHOLD、ADS、LW/R、READY和 WAIT和异步 FIFO的LA同步。

- 2)btog 地址二进制转换 Gray 码。

- 3)gtob 地址 Gray 码转换二进制。

- 4)地址比较和 FULL/EMPTY 产生逻辑 ,地址比较并产生FULL/EMPTY 信号。

- 5)控制逻辑 PCI9054 与 ARINC659 握手控制,并结合 FULL/EMPTY 信号,给出 PCI9054 和 ARINC659 对 DPRAM

使能信号 p\_en 和 rs\_en。

(2)DPRAM 模块 提供 2 套完整的读写控制单元,在各自的时钟节拍下读取 RAM 内容。

#### 5 仿真验证

对上述详细设计 Verilog 编码实现,结合 ARINC 659 接口芯片传输时序、DPRAM 的 FULL/EMPTY 的标识和支持PCI9054 4 种总线周期,设置仿真目的,如表 1 所示。仿真结果证明设计无误。

表 1 主要仿真条目

| 编号 | 仿真名称           | 期望操作            | 结果 |

|----|----------------|-----------------|----|

| 1  | 单步读仿真          | 单步读操作           | 正确 |

| 2  | 高地址未写单步读仿真     | 高地址读数无效         | 正确 |

| 3  | 连续读仿真(EMPTY=1) | 出现 EMPTY 后,读数无效 | 正确 |

| 4  | 连续读仿真(FULL=1)  | 出现 FULL 后,写数无效  | 正确 |

| 5  | 单步写仿真          | 单步写操作           | 正确 |

| 6  | 连续写仿真(EMPTY=1) | 出现 EMPTY 后,读数无效 | 正确 |

| 7  | 连续写仿真(FULL=1)  | 出现 FULL 后,写数无效  | 正确 |

#### 6 结束语

ARINC659 总线接口芯片采用同步器和异步 FIFO,较好地解决了与 PCI9054 芯片接口设计,并正确支持 PCI9054 要求的 4 种总线周期。此外,异步 FIFO 特性同时保证了 PCI9054 和 ARINC659 更灵活地收发数据且支持突发数据的收发,对后期的性能改进提供了足够的空间。仿真结果显示,异步 FIFO 正确解决了 ARINC659 与 PCI9054 之间的跨时钟数据传输。

#### 参考文献

- Airlines Electronic Engineering Committee. Backplane Data Bus, ARINC 659 Specification[M]. Annapolis, USA: Aeronautical Radio Inc., 1993.

- [2] 徐文辉. ARINC659 总线简介[J]. 航空电子技术, 1999, (2): 22-27.

- [3] 魏 芳, 刘志军, 马克杰. 基于 VerilogHDL 的异步 FIFO 设计与 实现[J]. 电子技术应用, 2006, (7): 97-99.

- [4] 汪 东, 马剑武, 陈书明. 基于 Gray 码的异步 FIFO 接口技术及 其应用[J]. 计算机工程与科学, 2005, 27(1): 58-60.

编辑 索书志

# (上接第 208 页)

### 参考文献

- [1] 曾 春, 邢春晓, 周立柱. 个性化服务技术综述[J]. 软件学报, 2002, 13(10): 1952-1961.

- [2] 徐 翔, 王煦法. 协同过滤算法中的相似度优化方法[J]. 计算机工程, 2010, 36(6): 52-54.

- [3] Claypool M, Le P, Waseda M, et al. Implicit Interest Indicators[C]// Proc. of ACM Intelligent User Interfaces Conference. New York, USA: ACM Press, 2001.

- [4] 余小高, 余小鹏. 基于隐式评分的推荐系统研究[J]. 计算机应用,

2009, 29(6): 1585-1589.

- [5] Shen Lei, Zhou Yiming, Xu Chao, et al, Predicting User Behavior in E-commerce Based on Psychology Model[C]//Proc. of the 6th International Conference on Fuzzy Systems and Knowledge Discovery. Washington D. C., USA: IEEE Computer Society, 2009.

- [6] Glasman L R, Albarracin D. Forming Attitudes That Predict Future Behavior: A Mete-analysis of the Attitude-behavior Relation[J]. Psychological Bulletin, 2006, 132(5): 778-822.

编辑 顾姣健