随着物联网产业市场的扩大, 大量新兴的物联网应用走进人们的生活中, 密码片上系统(System on Chip, SoC)的安全性问题越发凸显。密码SoC作为物联网安全的硬件基础设施, 其应对非侵入、半侵入和侵入式分析的抵御能力, 将直接影响物联网系统的物理层安全。在侵入式方向, 密码SoC的安全性需要具备完善的抵御措施, 应对安全传感器旁路、随机数发生器切割失效、数据总线探针等多种攻击手段[1-3]。相比于非侵入式和半侵入式分析, 侵入式物理分析所需设备更加昂贵, 例如原子力显微镜(AFM)、聚焦离子束(FIB)、研磨抛光设备等高端设备。此外, 部分侵入式分析平台对安全分析人员的技术水平提出了更加综合和专业化的要求[1], 分析员通常需要具备化学、微电子、材料学以及数学等多维度的知识[4-6]。

针对密码SoC片内存储器总线的探针分析, 是侵入式分析(攻击)中最直接获取敏感信息(如密钥、关键数据)的方法。攻击者首先除去SoC的封装, 然后将芯片敏感信号引出至芯片表面, 并通过预留焊盘打通实现与外界的信号连接, 从而使用微探针获取感兴趣的信号, 监听芯片内存储器访存时收发的敏感信息。

如果存储器总线布线在芯片顶层, 攻击者可直接采用微探针探测存储器的数据总线节点, 监听并获取芯片所保护的敏感信息; 如果采用具备表层主动防护层的安全布线, 布置在下层, 攻击者通常会使用FIB离子束对芯片进行打孔、切割、连接和引出, 旁路主动防护层传感器使其失效[3], 进一步采用微探针进行监听探测[7-9]。此外, 攻击者还可借助电子显微镜、AFM等高倍成像显微镜研究存储器的介质阵列, 对存储内容进行解读。

针对上述侵入式攻击手段, 密码SoC需要对片上数据存储总线进行加密保护, 例如对RAM、EEPROM、Flash等所存储的信息进行加密处理, 保障存储器的访存端口信号为加密信号, 而明文信号节点打散布局布线, 隐藏在大规模设计中, 从而确保存储器介质内容即便被攻击者观测, 也无法对其进行解读。本文提出一种基于LBlock算法的密码SoC存储加密总线, 将LBlock算法轮次在时序上进行压缩, 以降低时序代价, 提高访存效率。

1 方案设计为抵御侵入式的物理探测针对存储器周边敏感信号线的探测, 需要保障存储器直连的周边节点或连线为加密后的信息, 而加密前的明文信息节点则乱序、打散布局在芯片的各个金属层, 并且不出现在顶层, 根据当前主流的90 nm以下的工艺密度, 从数以亿计的打散信号中准确探测到加密前的明文电路节点并不现实。这样保障了存储介质被显微镜观测分析不可解读, 并且无法通过FIB和微探针探测存储器周边节点, 无法监听及获取明文数据。

加密算法选择受80位密钥控制、64位输入输出的LBlock算法, 一方面该算法结构简单, 关键路径短, 利于通过电路展开压缩执行时间, 提升访存吞吐率; 另一方面, 该算法强度经过长期论证[10-13], 加密分组为64位, 降低了32位总线直接加密被穷举的风险。

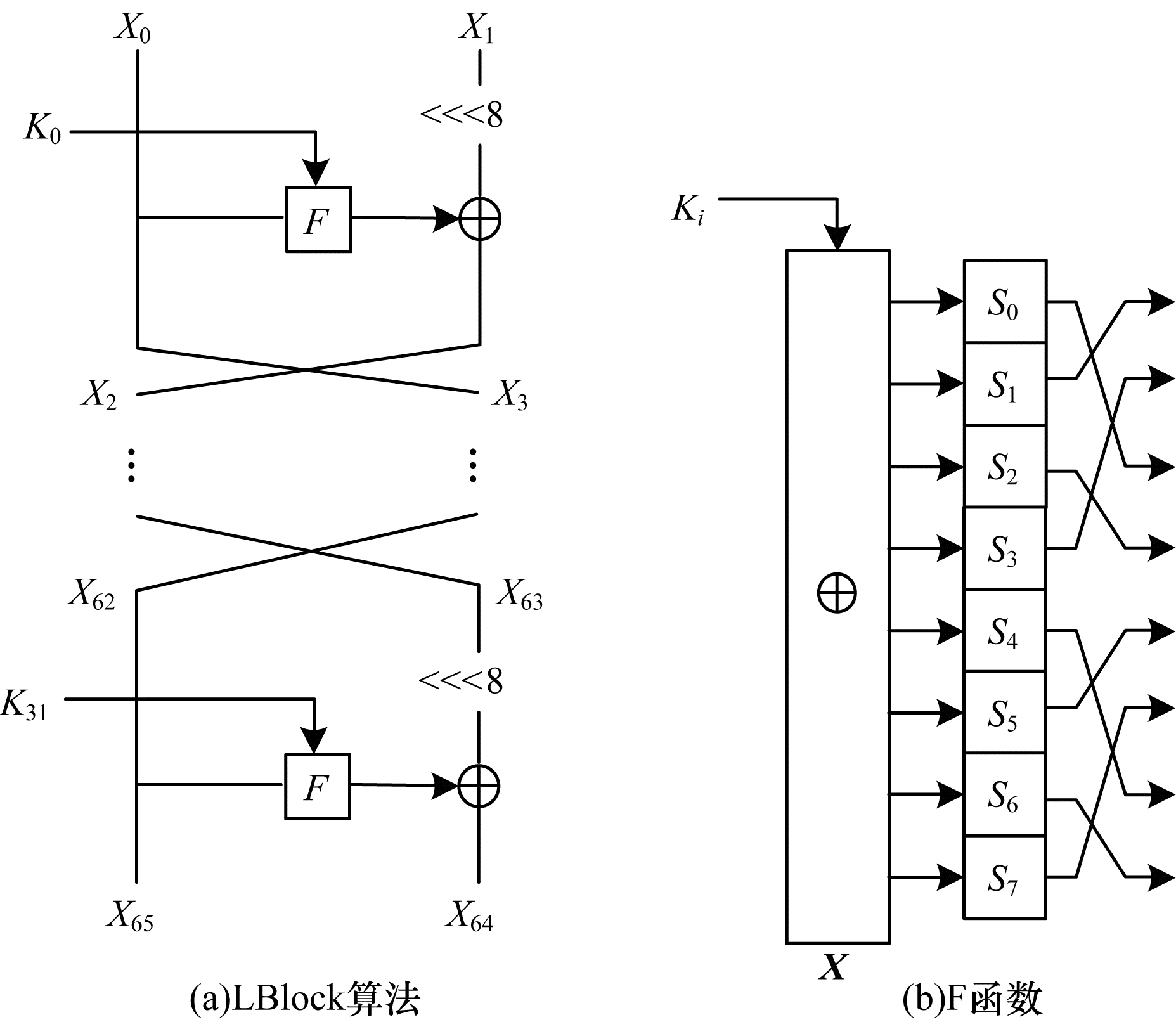

1.1 LBlock算法结构LBlock算法[14]属于轻量级分组密码算法, 受到国际密码学界的广泛关注, 具有较高的软硬件实现效率。其分组长度为64位, 密钥长度为80位, 采用32轮变体Feistel结构。图 1(a)为算法整体流程, 算法将64位明文分成左右两部各32位, 进行32轮运算后仍得出左右两部各32位, 共64位密文输出。图 1(b)给出图 1(a)中F函数的算法描述, 32位输入与子密钥Ki异或后, 每4位一组进入8个4进4出的S盒, 输出后需按图 1(b)中的排序进行换位。

|

Download:

|

| 图 1 LBlock算法 | |

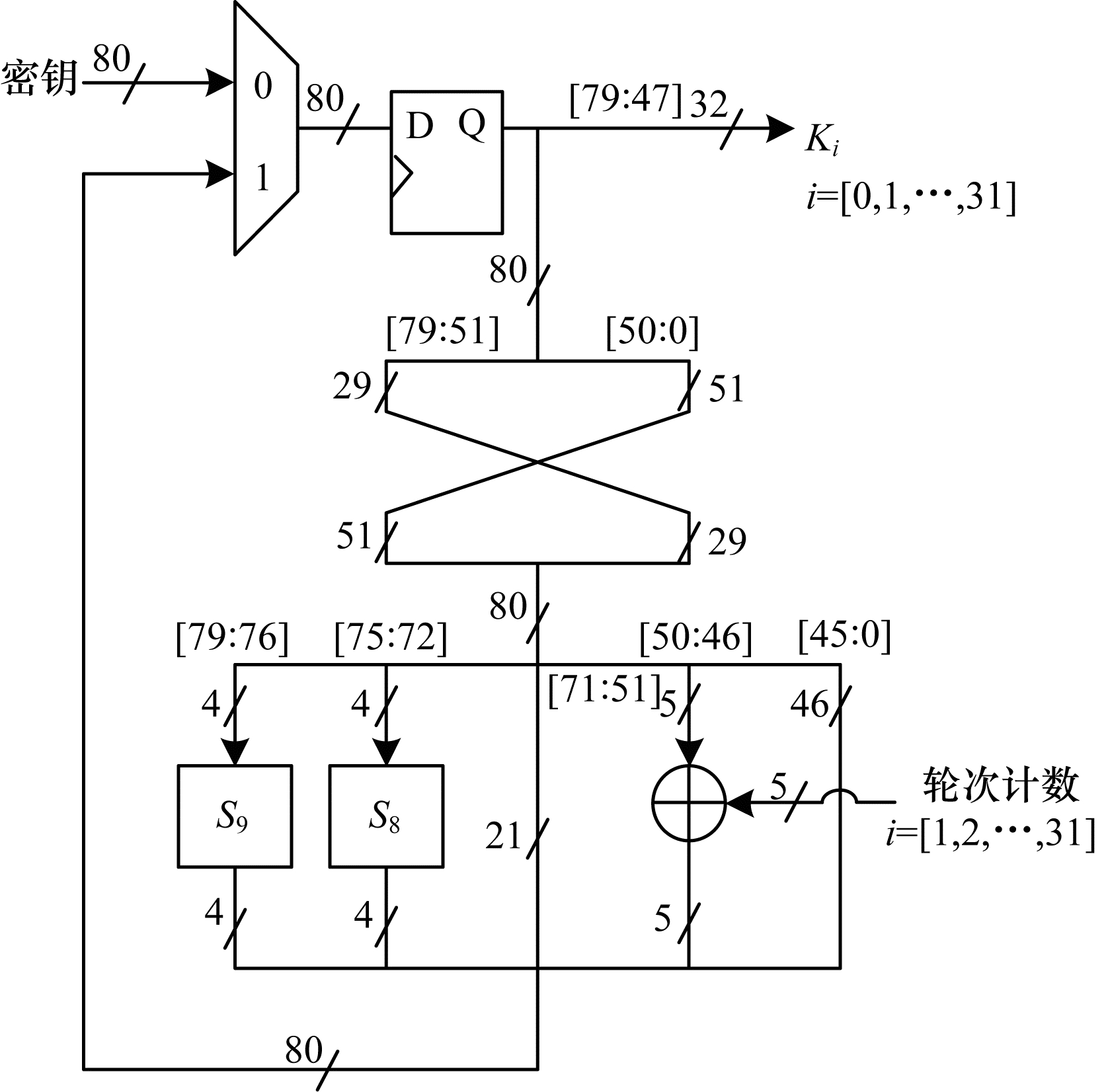

密钥扩展将80位主密钥取高32位作为轮密钥Ki(i=0, 1, …, 31), 每取一次轮密钥按以下步骤更新Ki:

1)[k79k78…k0]=[k50k49…k0k79k78…k51];

2)[k79k78k77k76]=S9[k79k78k77k76], [k75k74k73k72]=S8[k75k74k73k72];

3)[k50k49k48k47k46]=[k50k49k48k47k46]⊕[i]2。

其中, S8、S9均为4比特S盒。LBlock算法所涉及S盒标准参照LBlock算法标准, 皆为4比特类型。

解密仍采用图 1的操作, 仅需将明文替换为密文, 子密钥出现次序改为逆序Ki(i=31, 30, …, 0)。

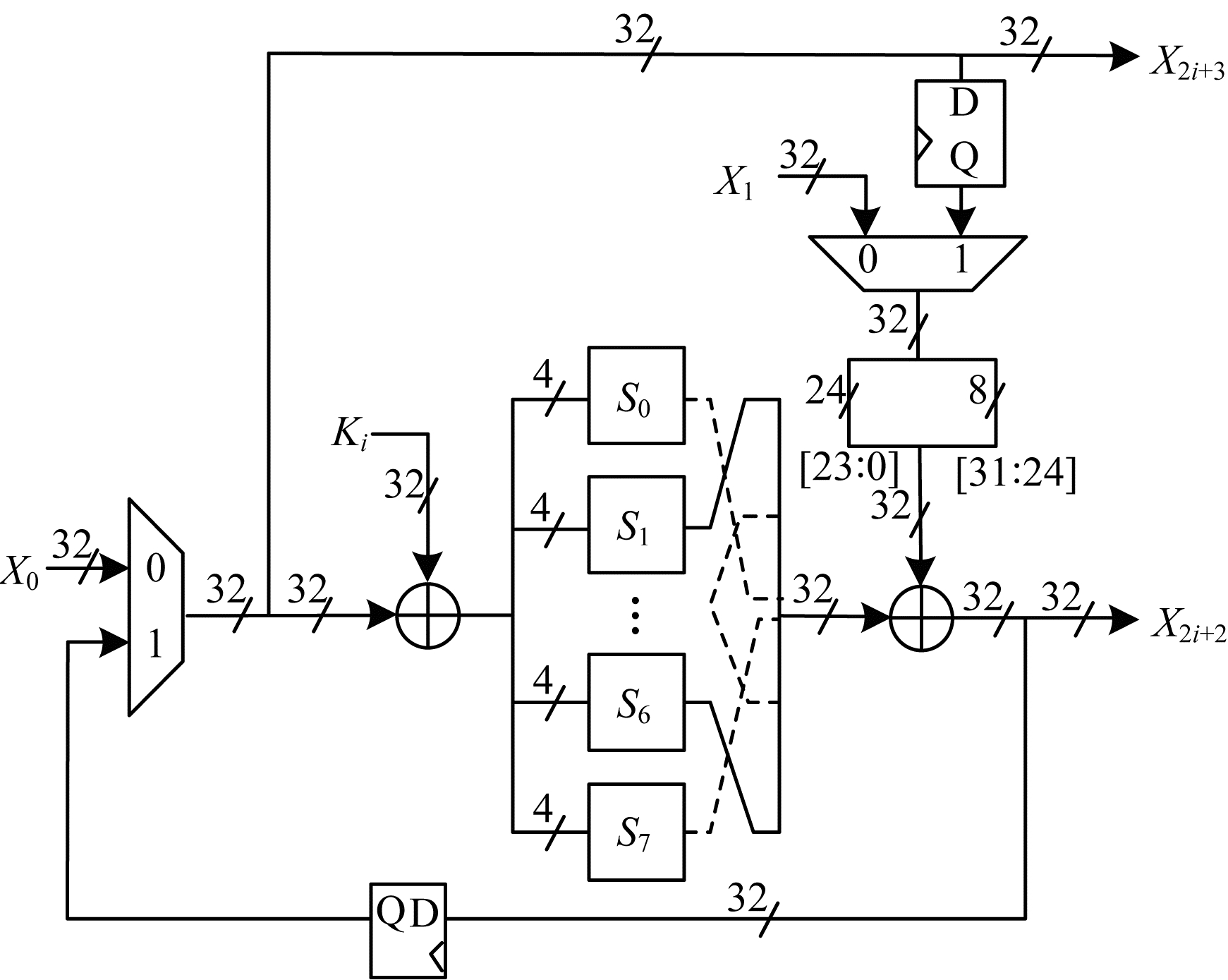

1.2 算法实现结构加密电路的数据路径如图 2所示。当加密轮次为首轮(i=0)时, 图 2中两个二选一MUX电路的“0”端选通, X0与X1两个32位明文信号输入至电路, 分别得到X2与X3; 此后的轮次二选一MUX的“1”端选通, 第i轮(i=1, 2, …, 31)运算得到X2i+2与X2i+3, 第32轮(i=31)输出X65与X64为64位密文[X65‖X64]。

|

Download:

|

| 图 2 加密电路的数据路径设计 | |

图 3为密钥扩展电路的数据路径设计。当加密轮次为首轮(i=0)时, 二选一MUX电路的“0”端选通, 同时直接取主密钥的高32位作为首轮子密钥K0; 此后轮次二选一MUX电路的“1”端选通, 第i轮(i=1, 2, …, 31)密钥扩展得到子密钥Ki。

|

Download:

|

| 图 3 密钥扩展电路的数据路径设计 | |

除密钥的安全存储外, 密码总线中所有电路不应借助片上易失或非易失存储空间存储, 因为这些空间本身也需受到该密码总线的加密存储保护。

加密密钥应在非易失性存储体中受保护的空间内存储, 在芯片生产或发行时写入, 只允许密码总线以硬件连接方式载入, CPU等其他电路不可访问。

解密电路的数据路径与加密电路一致, 仅将输入变为密文。解密时通常需要将密钥扩展的每一轮子密钥寄存然后逆序使用, 这并不适用于密码总线, 因为需占用的存储空间(通常为RAM空间)本身也应受该加密算法保护。本文方案解密时可将K31所在的最后一轮80位密钥, 在生产或发行时存储在非易失存储体中受保护的空间, 然后每一轮进行密钥扩展的逆运算, 如此可得K30, K29, …, K0。逆扩展中4比特S盒应取S8、S9的逆S8-1、S9-1。如此, 密钥扩展在加密与解密为两个不同电路, 且时序完全相同。4比特S盒的实现可直接采用真值表的组合逻辑描述, 利用综合工具的逻辑优化能力, 得到最优关键路径的组合逻辑电路。相比于DES算法的6比特S盒和AES算法8比特S盒, LBlock算法普遍采用4比特S盒, 其关键路径大幅缩短, 且在算法中配置更加灵活, 面积更加紧凑。

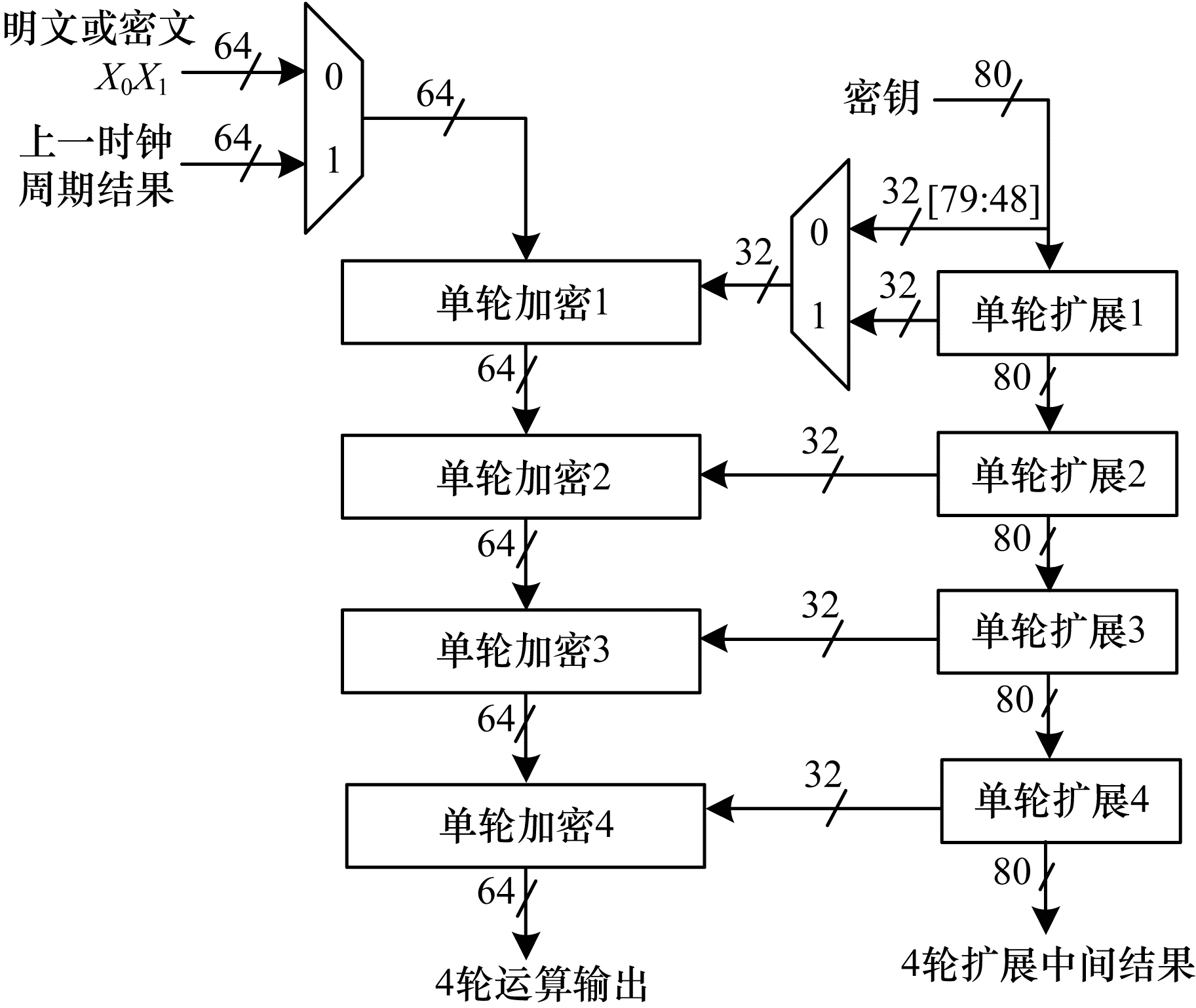

1.3 密码总线VLSI设计基于LBlock算法的VLSI结构的优点是数据路径非常短, 结构简练且具有较好的密码强度。但在时序上每次加密或解密需要进行32轮, 也即完成一个分组加解密需要32个时钟周期, 这对于存储读写总线的实时性和吞吐率会带来较大的影响。所以, 可将密码VLSI结构进行展开, 每个时钟完成4个~8个轮次, 加快密码总线读写性能。图 4给出单时钟4轮次展开电路结构, 该结构下一个时钟周期可完成4轮加密, 共8个时钟周期完成加密, 其中加解密第一个时钟周期中二选一MUX电路“0”端选通, 其余时钟周期“1”端选通。

|

Download:

|

| 图 4 4时钟时序展开电路结构 | |

相比于32轮标准实现, 4时钟时序展开电路信号输入设计只需少量调整, 单轮加密1模块、单轮扩展1模块参照图 2和图 3, 分别取消二选一MUX和寄存器(DQ触发器), 然后将单轮输出分别引向下一轮单轮加密2模块、单轮扩展2模块, 以此类推, 时序展开设计非常便捷。如此每个时钟周期得到4轮运算结果和密钥扩展结果, 8个时钟完成加解密。

本文设计采用4轮叠加的时序展开结构, 关键路径延迟会相应增加, 这主要考虑到LBlock算法为轻量级算法, 其单轮次关键路径延迟低于1 ns。4时序展开后, 由于综合工具的逻辑优化能力, 总延迟仅为3 ns左右, 在100 MHz时钟频率下具有足够的时序裕量, 满足当前密码SoC的主流频率约束。

2 验证结果与性能分析总线位宽一般为8位、16位或者32位, 如选择32位或以下分组的加密算法, 因密码本空间不足, 会遭受直接穷举攻击。LBlock密码算法分组长度为64位, 在总线挂接设计时, 需设计缓冲Buffer机制将总线单拍信息(8位、16位或32位)填充至64位再加密, 无法凑整时应填充随机数凑整。

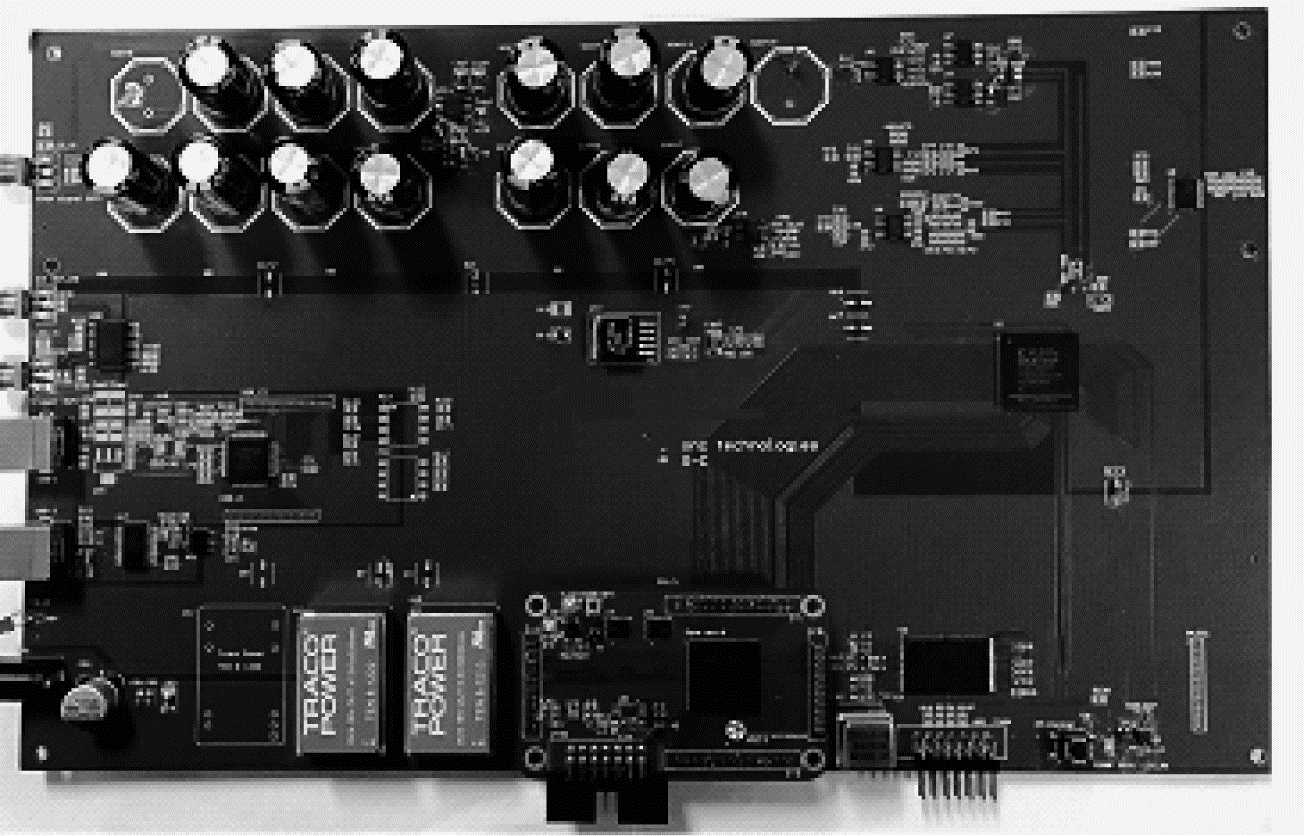

在Manis测试验证平台上进行设计验证, FPGA型号为Spartan-3E xc3s1400A, 采用Verilog硬件描述语言实现本文所述的4时钟时序展开密码总线, 总线位宽32位, 在50 MHz时钟频率下, 连续地址加密写和解密读数据吞吐率达到266 Mb/s。FPGA平台环境如图 5所示。

|

Download:

|

| 图 5 FPGA验证平台 | |

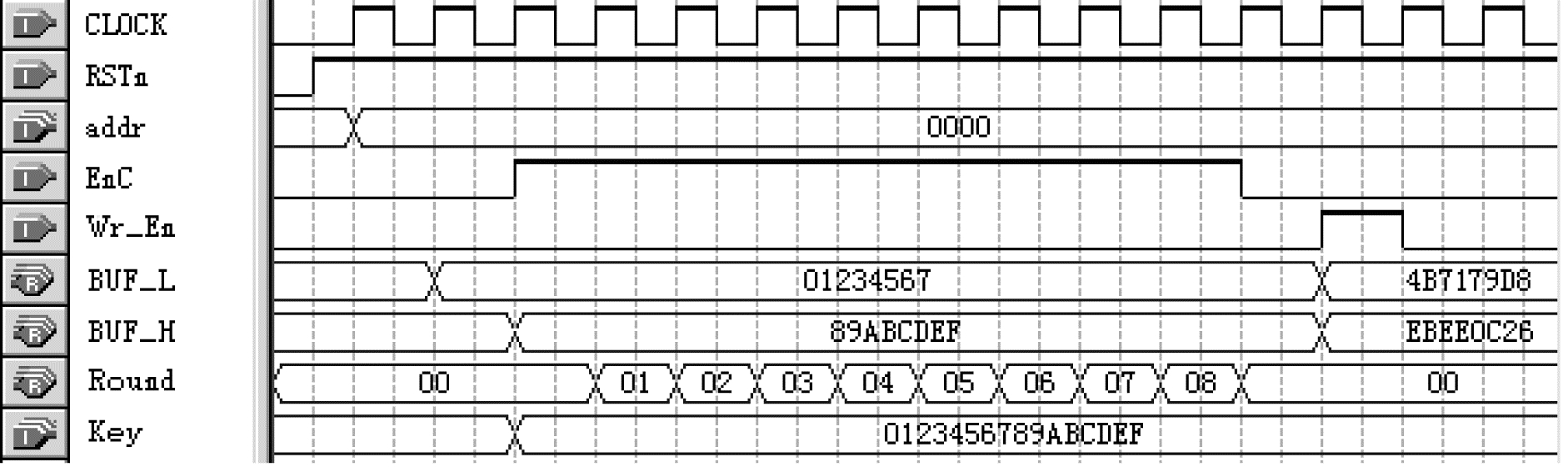

图 6为向地址0x0000的存储空间写入64位数据0x0123456789abcdef的过程, Round寄存器用于8时钟计数, 密钥也同为0x0123456789abcdef。通过对访问缓冲区BUF_L和BUF_H的控制, 得到写入密文为0x4b7179d8ebee0c26, 批量写入可进行依次流水操作。读出时使用时序相同的解密电路对存储密文进行解密。

|

Download:

|

| 图 6 密码存储总线设计时序 | |

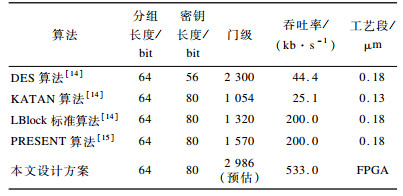

表 1给出本文设计方案与其他轻量级算法实现性能对比[14-15], 标准32轮LBlock实现在较低门级下具备较好性能, 相比之下本文方案采用4时序展开技术, 在门级增加约一倍的情况下, 将连续访存性能再提高近2.7倍, 时钟频率为100 KHz时峰值速率达到533 kb/s, 这说明本文方案吞吐率性能更加匹配SoC存储总线的性能需求。此外, 本文方案采用FPGA实现, 门级为预估所得, 需指出的是, 在当前流行的40 nm~90 nm工艺段, 2 000门级以下的代价增加成本低于¢1。

|

下载CSV 表 1 各轻量级算法实现性能对比 |

| [1] |

TORRANCE R, JAMES D.The state-of-the-art in IC reverse engineering[C]//Proceedings of International Workshop on Cryptographic Hardware and Embedded Systems.Berlin, Germany: Springer, 2009: 363-381.

(  0) 0)

|

| [2] |

SAMYDE D, SKOROBOGATOV S, ANDERSON R, et al.On a new way to read data from memory[C]//Proceedings of the 1st International IEEE Security in Storage Workshop.Washington D.C., USA: IEEE Press, 2002: 65-69.

(  0) 0)

|

| [3] |

CIORANESCO J M, DANGER J L, GRABA T, et al.Cryptographically secure shields[C]//Proceedings of 2014 IEEE International Symposium on Hardware-oriented Security and Trust.Washington D.C., USA: IEEE Press, 2014: 25-31.

(  0) 0)

|

| [4] |

WEINGART S H.Physical security devices for computer subsystems: a survey of attacks and defenses[C]//Proceedings of International Workshop on Cryptographic Hardware and Embedded Systems.Berlin, Germany: Springer, 2000: 302-317.

(  0) 0)

|

| [5] |

SKOROBOGATOV S. Physical attacks and tamper resistance[M]. Berlin, Germany: Springer, 2012.

(  0) 0)

|

| [6] |

冉彤, 白国强. 基于系统级封装(SiP)的信息安全芯片集成设计[J]. 微电子学与计算机, 2012, 29(1): 10-14. (  0) 0)

|

| [7] |

SHAHRJERDI D, RAJENDRAN J, GARG S, et al.Shielding and securing integrated circuits with sensors[C]//Proceedings of 2014 IEEE/ACM International Conference on Computer-Aided Design.Washington D.C., USA: IEEE Press, 2014: 170-174.

(  0) 0)

|

| [8] |

BRIAIS S, CIORANESCO J M, DANGER J L, et al.Random active shield[C]//Proceedings of 2012 Workshop on Fault Diagnosis and Tolerance in Cryptography.Washington D.C., USA: IEEE Press, 2012: 103-113.

(  0) 0)

|

| [9] |

BRIAIS S, CARON S, CIORANESCO J M, et al.3D hardware canaries[C]//Proceedings of International Workshop on Cryptographic Hardware and Embedded Systems.Berlin, Germany: Springer, 2012: 1-22.

(  0) 0)

|

| [10] |

黄永洪, 郭建胜, 罗伟. LBlock算法的相关密钥不可能差分攻击[J]. 电子学报, 2015, 43(10): 1948-1953. DOI:10.3969/j.issn.0372-2112.2015.10.011 (  0) 0)

|

| [11] |

ZHANG Huiling, WU Wenling.Structural evaluation for generalized feistel structures and applications to LBlock and TWINE[C]//Proceedings of the INDOCRYPT'15.Berlin, Germany: Springer, 2015: 218-237.

(  0) 0)

|

| [12] |

BOURA C, NAYA-PLASENCIA M, SUDER V.Scrutinizing and improving impossible differential attacks: applications to CLEFIA, Camellia, LBlock and Simon[C]//Proceedings of ASIACRYPT'14.Berlin, Germany: Springer, 2014: 179-199.

(  0) 0)

|

| [13] |

郑雅菲, 吴文玲. LBlock算法的改进中间相遇攻击[J]. 计算机学报, 2017, 40(5): 1080-1091. (  0) 0)

|

| [14] |

WU Wenling, ZHANG Lei.LBlock: a lightweight block cipher[C]//Proceedings of International Conference on Applied Cryptography and Network Security.Berlin, Germany: Springer, 2011: 327-344.

(  0) 0)

|

| [15] |

BOGDANOV A, KNUDSEN L R, LEANDER G, et al.PRESENT: an ultra-lightweight block cipher[C]//Proceedings of International Workshop on Cryptographic Hardware and Embedded Systems.Berlin, Germany: Springer, 2007: 450-466.

(  0) 0)

|

2019, Vol. 45

2019, Vol. 45