2. 广东工业大学 计算机学院, 广州 510006

2. Faulty of Computer, Guangdong University of Technology, Guangzhou 510006, China

开放科学(资源服务)标志码(OSID):

随着深度学习技术的快速发展,诸如智慧城市、智能医疗、无人驾驶、军事安防等场景,都在大量部署各种基于深度学习技术的设备。这些应用场景、对设备的功耗、延迟、资源利用、实时性等方面有严格的要求。利用通用的CPU和GPU设备实现这些应用往往不是最佳选择。与通用的CPU和GPU设备相比,专用的神经网络加速器,尤其是基于现场可编程门阵列(Field Programmable Gate Array,FPGA)平台设计的神经网络加速器,在性能、实时性、价格等方面具有优势。

对于卷积神经网络算法的研究,多数研究者的关注点在于提高模型的准确率。在此趋势下,卷积神经网络的层数和宽度不断加深,这导致参数和计算量越来越大,从而无法在各种功耗和性能受限的平台上运行。为解决这一问题,研究者提出了各种轻量化神经网络模型。轻量化神经网络模型是专门针对功耗和性能受限平台设计的轻量且高效的神经网络模型。相较于传统卷积神经网络,轻量化神经网络计算复杂度更低且参数规模大幅缩减,具有结构简单、运行速度快等显著优点。

目前大部分神经网络加速器仅支持实现低效率的卷积神经网络(如Alex Net和VGG16),并不支持以MobileNet为代表的轻量化神经网络。本文设计并实现面向轻量化网络MobileNet可配置的神经网络加速器。针对MobileNetV3的轻量化模块,加入优化的PW模块和DW模块,同时利用可配置化(指令)设计,实现通过修改上位机的程序支持各种不同的网络结构的功能。此外,通过8 bit定点、流水和并行化等优化技术,使加速器在资源利用、性能、功耗等方面更具优势。

1 相关工作基于FPGA的神经网络加速器设计是一个备受关注的课题。文献[1]设计了一个用于大规模图像分类的FPGA神经网络加速器;文献[2]通过重复输入特征图提高带宽利用率,改善了神经网络加速器;文献[3]提出以ping-pang方式调整缓存数据量,在一定程度上提升了卷积加速器的性能;文献[4]则提出软硬件协同设计方法;文献[5]考虑了DSP资源优化和卷积神经网络分类准确率的问题。

神经网络结构的轻量化也是目前备受关注的研究主题,轻量化网络结构在保证准确率的同时使得模型体积更小,速度更快。SqueezeNet[6]模型使用分解卷积核技术使得模型体积更小,速度更快;ShuffleNet模型[7]采用残差网络思想;而Xception模型[8]采用更改卷积运算流程降低计算量;MobileNet模型[9]采用逐通道卷积减少计算量。

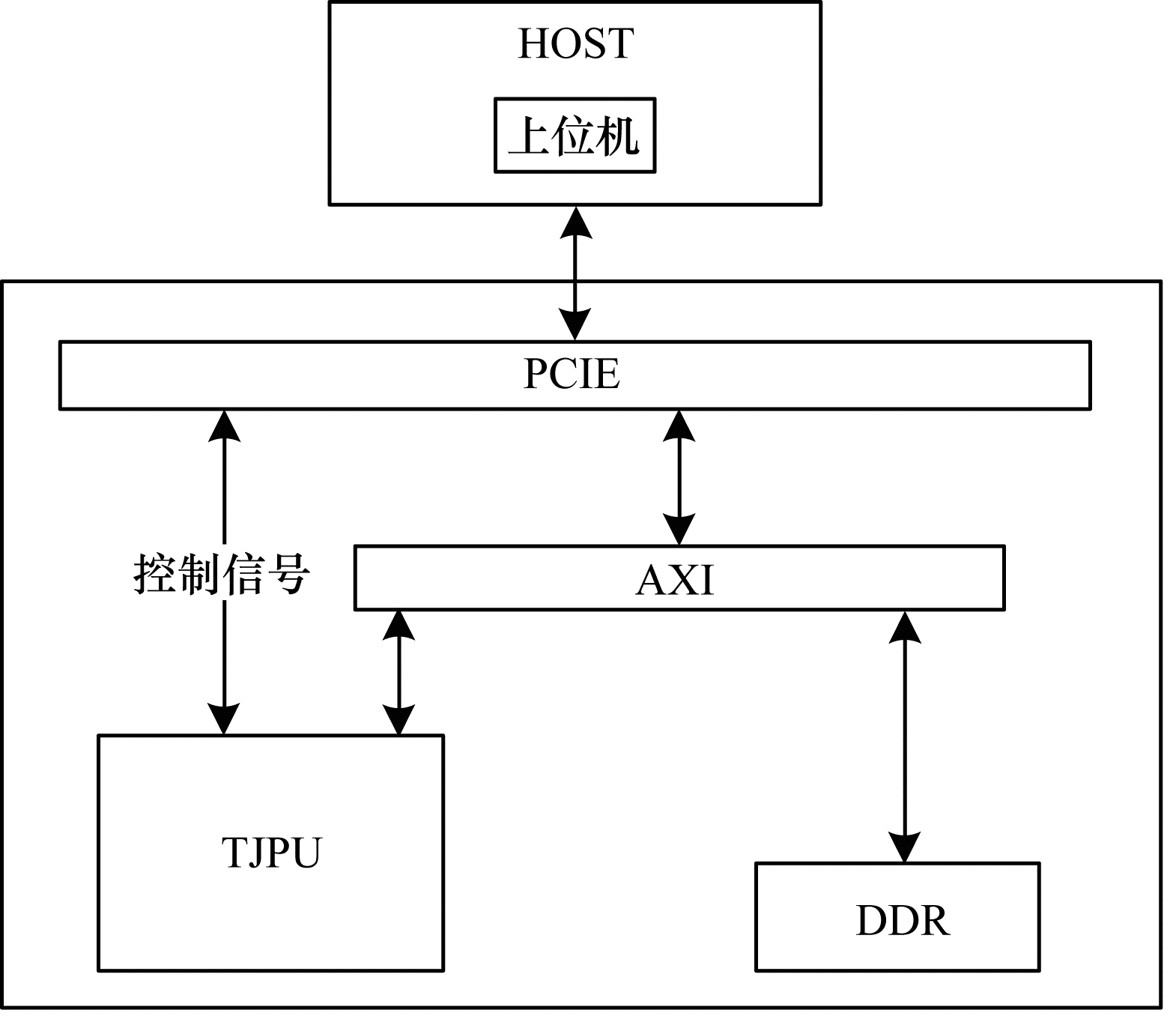

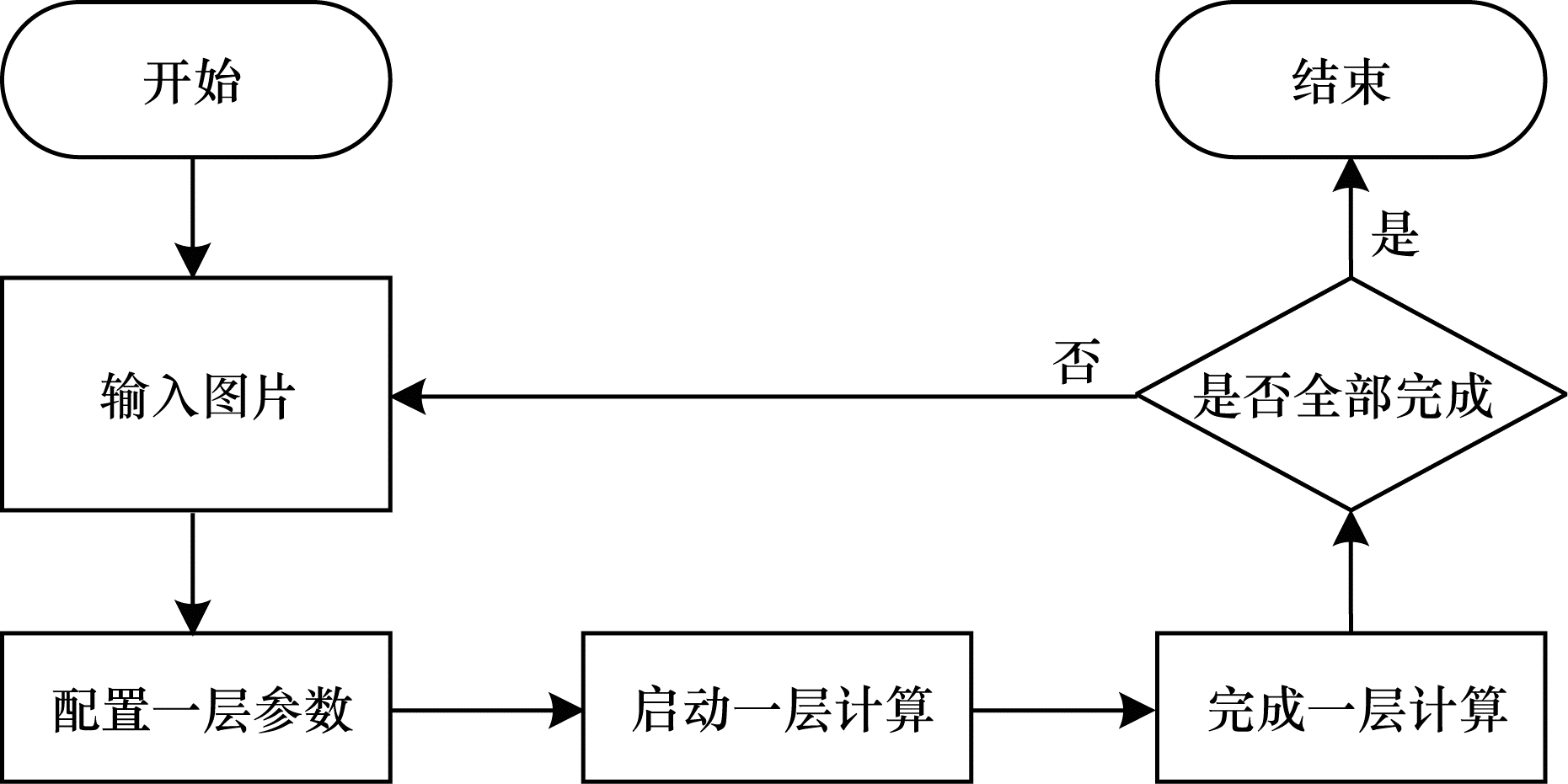

2 针对轻量化网络的可配置神经网络加速器 2.1 整体架构轻量化网络移植到资源受限的平台上具有巨大的优势,但为了满足实时性要求和资源利用最大化,本文针对轻量化网络模型设计软硬协同加速框架,如图 1所示,其中TJPU架构如图 2所示。

|

Download:

|

| 图 1 软硬协同加速框架 Fig. 1 Software and hardware coacceleration framework | |

|

Download:

|

| 图 2 TJPU架构 Fig. 2 Architecture of TJPU | |

在根据相互关系设计出软硬件协同加速框架中,软件部分负责计算任务的调度和控制,硬件部分负责计算数据。由于加速器的存储资源和计算资源有限,因此本文通过软件将轻量化神经网络模型中一层计算所需的参数经由PCIE存储到DDR中,图片数据通过上位机直接写入到计算单元TJPU中,计算出来的结果保存到DDR中。通过以一层计算为单位,减少模型对于硬件存储资源的需求。

2.2 轻量化算子MobileNet的基本单元是深度可分离卷积(Depthwise Separable Convolution,DSC),其可以分解为2个更小的操作,即Depthwise Convolution(DW)和Pointwise Convolution(PW)。DW负责通道卷积,PW负责串联feature map。这种方法比传统卷积减少8~9倍的计算量。

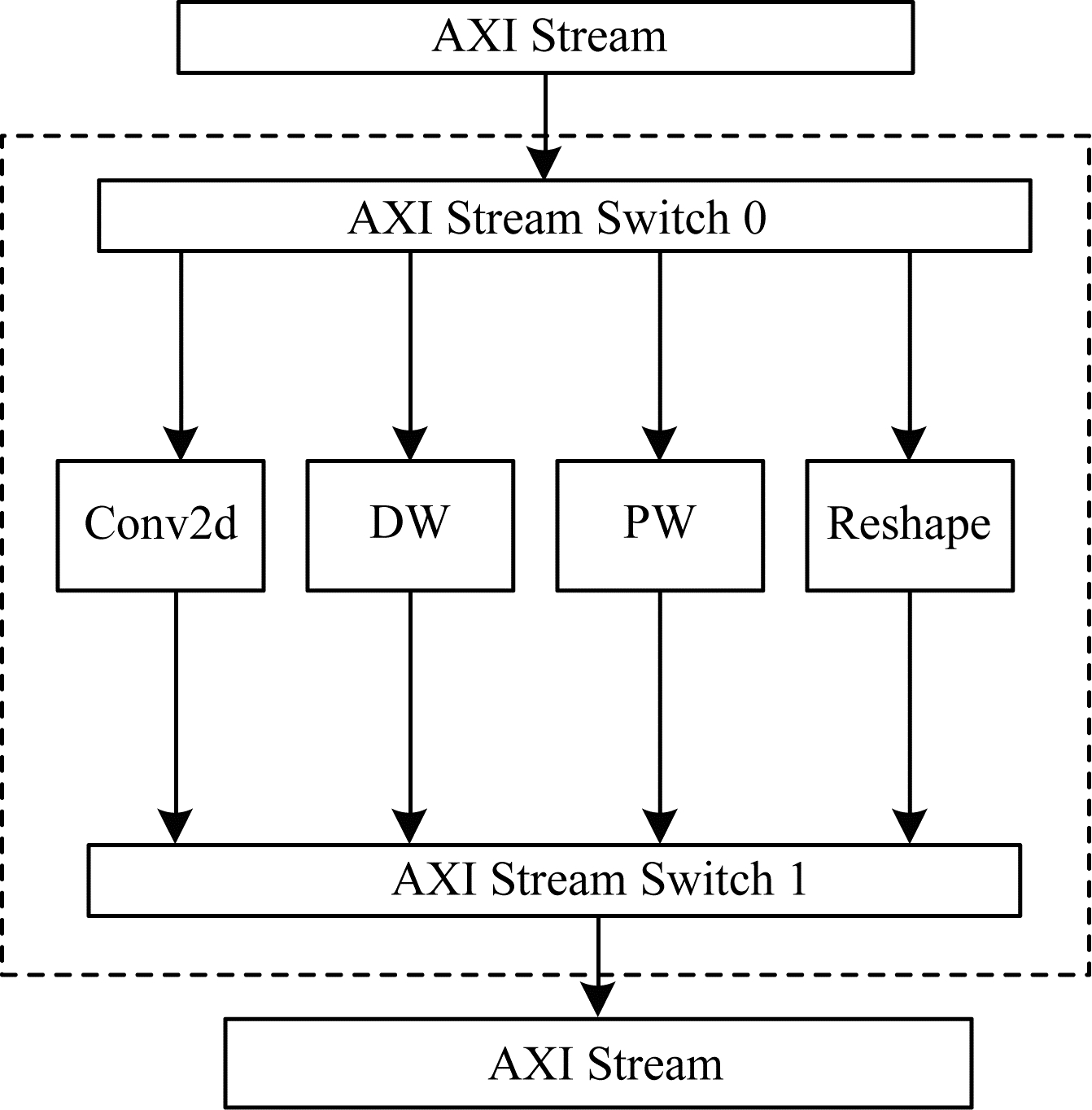

为支持MobileNet结构,本文设计的卷积算子分为Conv2d、PW、DW、Reshape 4个基本模块。通过软件不同的调度顺序,以实现不同轻量化神经网络模型的计算。当然,除了支持MobileNet结构外,其他由Conv2d、PW、DW和Reshape模块构成的网络结构都可以在该加速器中实现。

2.3 8 bit量化FPGA存储资源受限且不适合浮点运算,而正常训练的浮点神经网络模型进行推断,需要占用大量的计算资源,这对于AI处理器来说是难以适用的。因此,直接使用网络模型参数进行计算,不能在算力上发挥优势,加快模型推断速度。本文采用8 bit定点数,需要对浮点模型进行量化。量化方法主要用于压缩参数量和减少参数资源的占用量。在保证精度的前提下,使用INT8量化大幅缩减参数量,解决硬件平台存储资源受限问题。

线性量化公式如式(1)和式(2)所示。

| $ {X}_{\mathrm{i}\mathrm{n}\mathrm{t}}=\mathrm{r}\mathrm{o}\mathrm{u}\mathrm{n}\mathrm{d}\left(\frac{x}{S}\right)+Z $ | (1) |

| $ {X}_{\mathrm{Q}}=\mathrm{C}\mathrm{l}\mathrm{a}\mathrm{m}\mathrm{p}\left(0, {N}_{\mathrm{l}\mathrm{e}\mathrm{v}\mathrm{e}\mathrm{l}\mathrm{s}}-1, {X}_{\mathrm{i}\mathrm{n}\mathrm{t}}\right) $ | (2) |

其中:round(·)表示四舍五入处理;S表示缩放的系数;Z代表的是零点;Clamp代表截断操作;Nlevels由量化的位数决定,如8位则为28=256。线性量化公式的反量化公式为:

| $ {X}_{\mathrm{f}\mathrm{l}\mathrm{o}\mathrm{a}\mathrm{t}}=\left({X}_{\mathrm{Q}}-Z\right)S $ | (3) |

在进行卷积运算操作时,原卷积公式变为如下公式:

| $ {Q}_{3}^{\left(i, k\right)}={Z}_{3}+\frac{{S}_{1}{S}_{2}}{{S}_{3}}\sum\limits _{j=1}^{N}\left({Q}_{1}^{\left(i, j\right)}-{Z}_{1}\right)\left({Q}_{2}^{\left(i, j\right)}-{Z}_{2}\right) $ | (4) |

文献[10]中的实验结果表明,多数神经网络模型使用此方法进行8 bit数据量化造成的精度损失在3%以内。

2.4 并行与流水并行度优化和流水优化是常用的硬件优化策略,并行度优化是指将数据切分为多个部分进行并行化计算从而达到提高计算效率的目的。本文针对卷积的6个循环进行并行度的优化:1)同时计算4张图片;2)卷积展开,3×3卷积核直接用9个乘法器进行计算;3)输入通道和输出通道分块,按照8入通道8出通道进行并行,进一步增加其并行度。

在流水优化方面,采用ping-pang操作流水优化通过降低传播时延,提高系统频率和吞吐量,优化运行速度。ping-pang操作是利用数据缓存,将ping路数据处理完保存在pang路的缓存‵中,ping路可以继续处理上一级的数据,pang路无需等待,直接从缓存中读取数据进行处理。

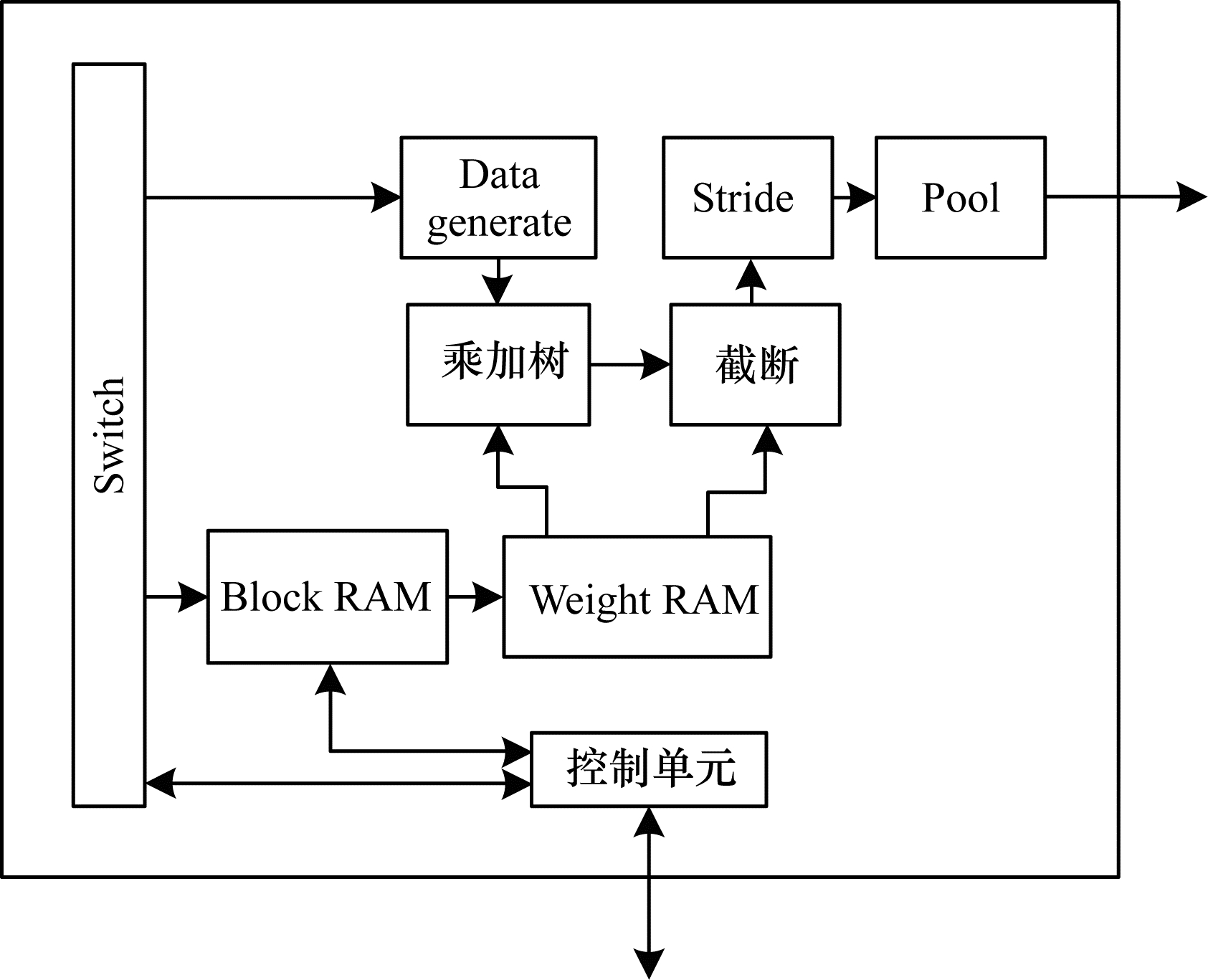

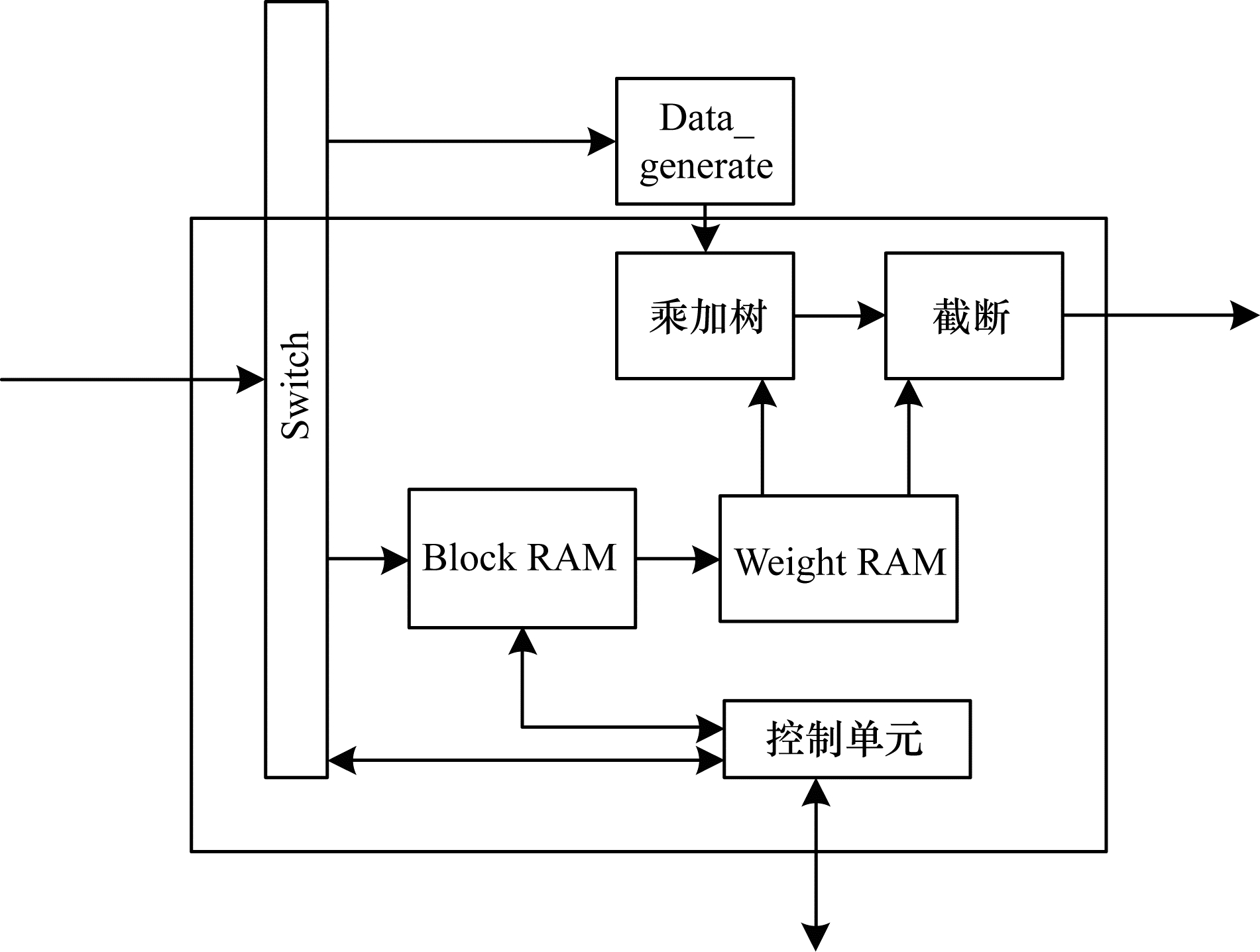

3 FPGA实现 3.1 Conv2d模块实现Conv2d模块的功能是实现通常的3×3卷积,如图 3所示,该模块由Switch、Block RAM、Weight RAM、控制单元、乘加树模块、截断、Data_generate、Stride、Pool等组成。在上位机指令的控制下,控制单元首先发出读数据操作,从DDR中将权重数据读入到Block RAM中;然后启动卷积计算,特征图的数据经过Data_generate模块,生成特定格式的数据,这些数据与已经读入的权重数据进行乘加操作;最后计算结果经过截断后,经过Stride和Pool后,输出到DDR中。这里需要注意的是,Stride和Pool可以通过上位机指令进行开关。当需要计算的卷积没有Stride或者Pool时,只需要在上位机配置即可。

|

Download:

|

| 图 3 Conv2d模块框图 Fig. 3 Block diagram of Conv2d module | |

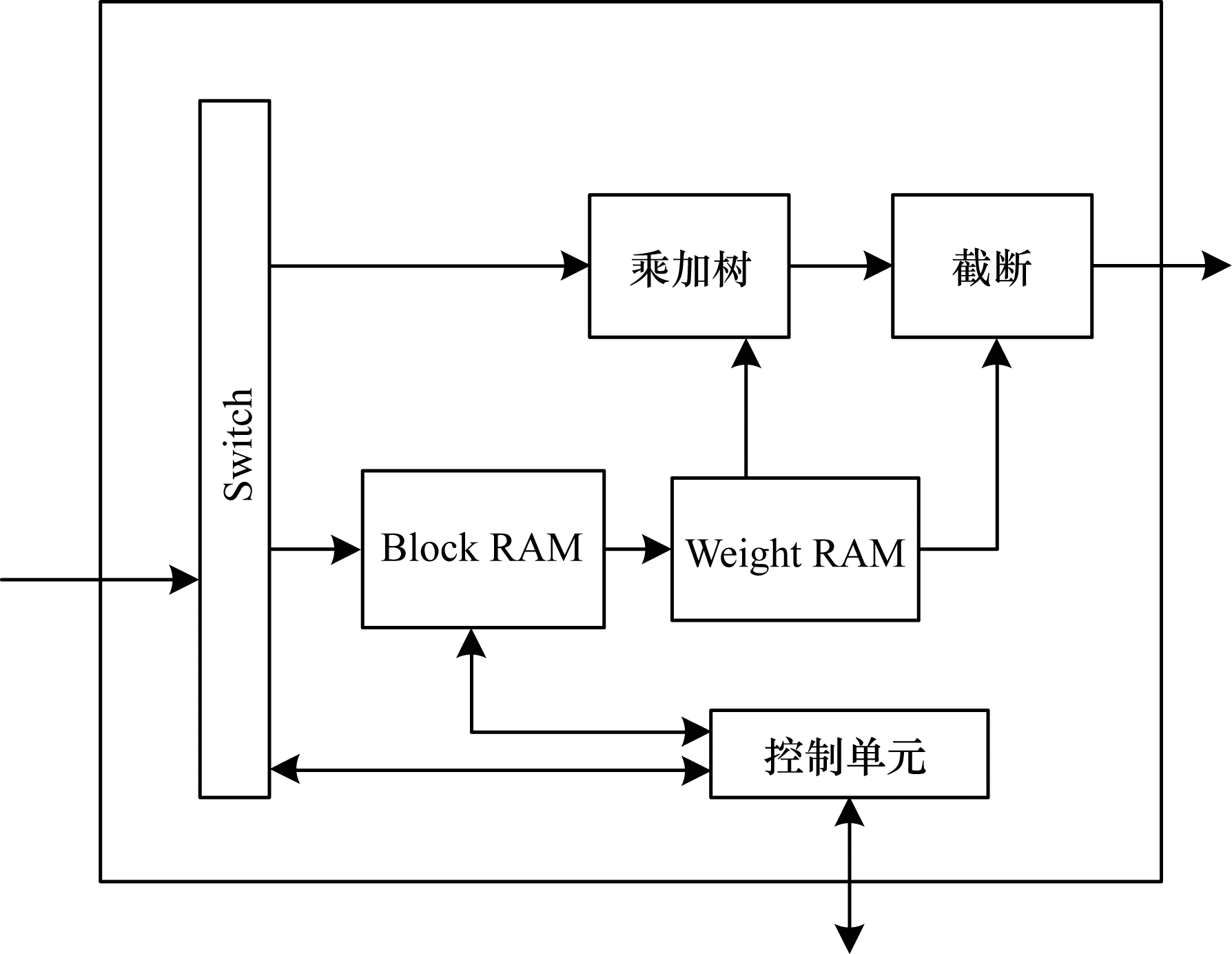

PW实现1×1卷积功能,采用通用框架设计。如图 4所示,该模块由Switch、Block RAM、Weight RAM、控制单元、乘加树、截断等组成。Switch模块是一个数据通路选择模块,控制数据流通,Bolck RAM模块存放计算参数,乘加树进行卷积乘法通道相加操作,截断模块进行量化操作。整个PW模块由不同功能模块进行灵活组合,提高复用率。整个模块通过上位机发送指令,由指令解析模块进行解析配置,PW控制单位完成数据通路选择和计算启动的控制。

|

Download:

|

| 图 4 PW模块框图 Fig. 4 Block diagram of PW module | |

DW模块完成深度卷积操作,与Cond2d类似,在MobileNet网络结构中DW模块无需进行Stride和Pool。根据上述分析,本文设计如图 5所示的DW模块。DW模块主要由Data_generate、Switch、Block RAM、Weight RAM、控制单元、乘加树模块、截断模块等结构组成。Data_generate模块将数据转换成可卷积的3行数据,其他模块由PW模块中的功能模块组成,完成DW模块所需的功能。

|

Download:

|

| 图 5 DW模块框图 Fig. 5 Block diagram of DW module | |

Reshape模块主要完成数据的重排操作,MobileNet结构需要完成Contact和Upsample 2种数据重排操作。因此,如图 6所示,Reshape模块由2个Switch、Block RAM模块、Weight RAM、Contact、Upsample等结构组成。数据通过Switch进行选择,如果配置为Upsample功能,数据将会流入到Upsample模块中,进行Upsample操作后,数据通过Switch写入DDR。如果配置为contact功能,那么数据就会分成两路通过Switch分别进入到Contact和BlockRam,进行Contact操作后,写入DDR。

|

Download:

|

| 图 6 Reshape模块框图 Fig. 6 Block diagram of Reshape module | |

AI处理器指令集[11-13]在设计上满足轻量化网络模型通用配置。因为要考虑轻量化网络模型的兼容性,所以指令集的设计采用精简指令集。指令集包含参数配置指令、计算配置指令等。

上位机通过配置指令集,调度AI处理器内部卷积算子的运算[14-16]。由于片上资源有限,为解决计算量庞大问题,上位机调度采用一层计算为一个单元进行调度,从而减少参数占用资源,降低计算量,同时使得轻量化网络模型更加通用化配置。

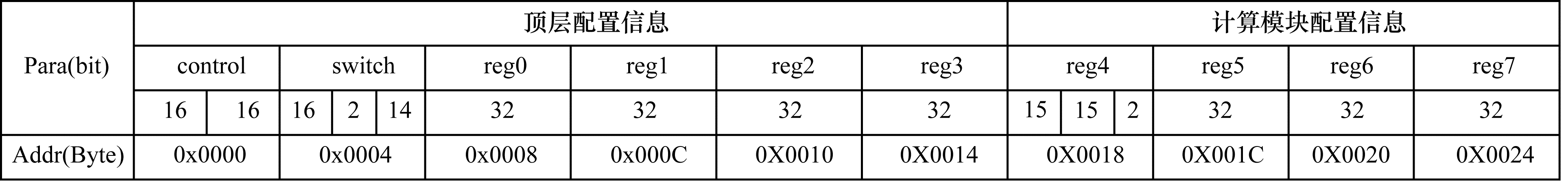

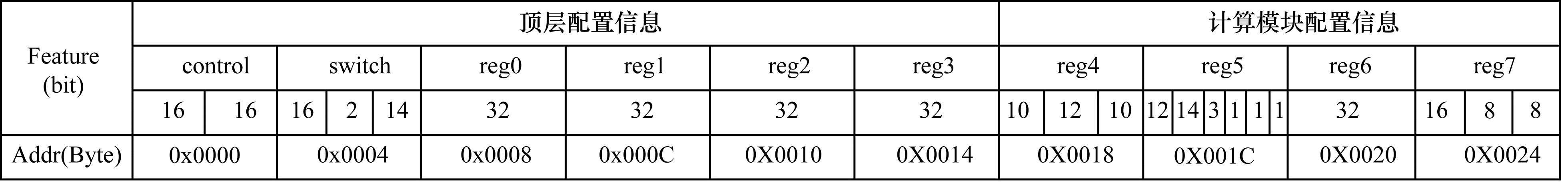

4.1 指令集设计指令集设计采用精简指令设计方法,顶层指令控制模块类似一个仲裁器,其不进行复杂的控制。由于计算流程的控制上移到软件,各个模块的控制主要在自己模块内部,因此顶层控制模块只是控制数据的通路[17],上位机启动功能模块的运行,根据结束后功能模块的返回信号,启动DMA的读写。逻辑的正确性保证完全来自于上位机如图 7和图 8所示,顶层指令控制模块包含Padding、Stride、Row_num、Channel_num等参数,配置卷积模块所需的计算参数和启动信号,同时配置参数指令和配置计算指令共享reg4和reg5寄存器,由此优化寄存器空间,降低资源使用率。

|

Download:

|

| 图 7 顶层配置指令 Fig. 7 Top-level configuration instruction | |

|

Download:

|

| 图 8 计算配置指令 Fig. 8 Calculation configuration instruction | |

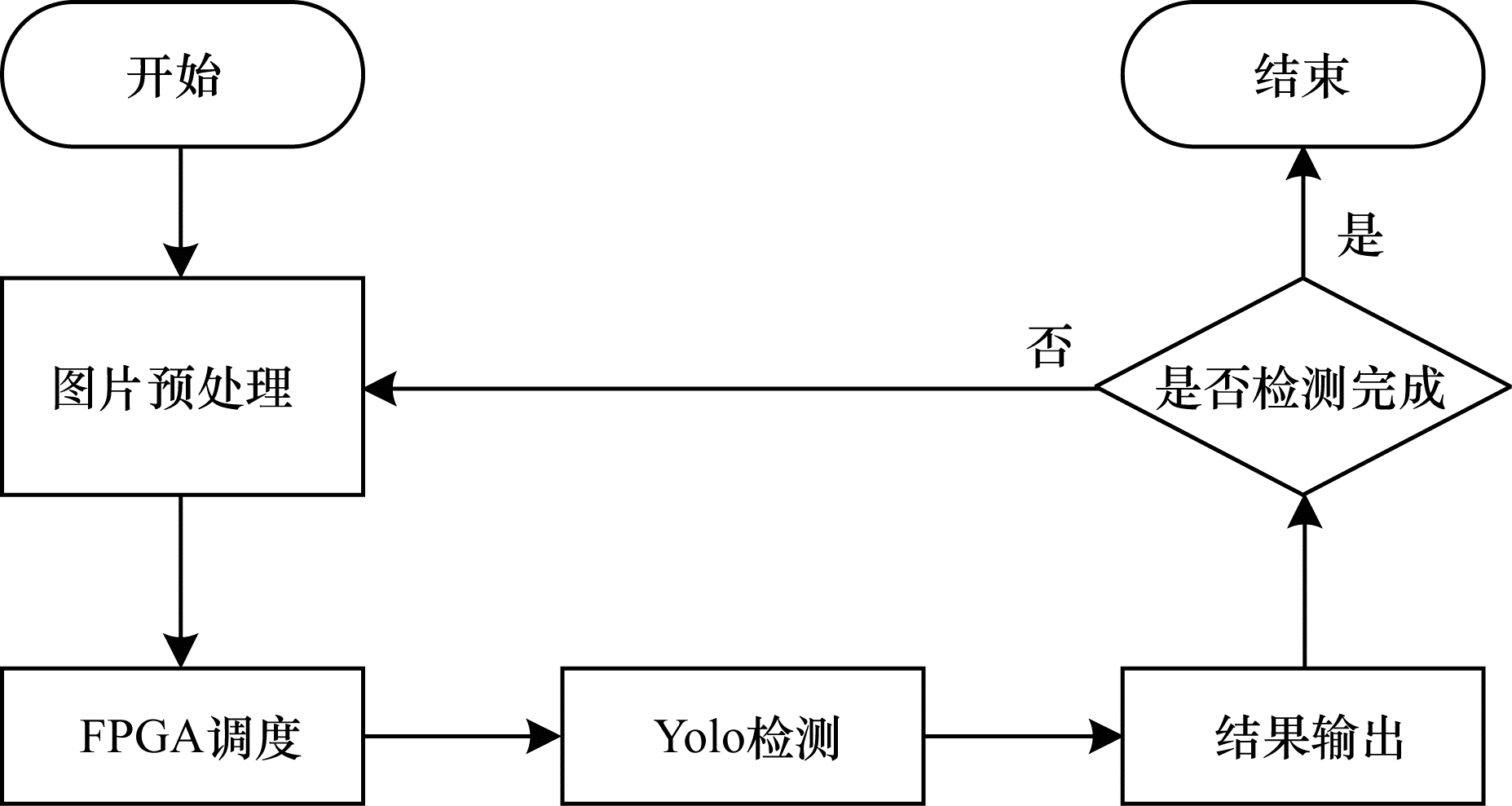

上位机采用C++语言编写,主要实现图片的预处理、Yolo层的检测(主要计算为非极大值抑制)、检测结果、输出和FPGA的任务调度[18-19]等功能。图片预处理部分的任务有图像的读取/视频抽帧、图像缩放等。这部分需要借助OpenCV等图像/视频处理库实现,其操作的类型繁多。Yolo算法检测部分主要为特征向量的提取、非极大值抑制等,这些操作都是串行的操作,在主机上能够非常高效地完成。检测结果的输出(包括画框等)也是串行计算。除了上述任务之外,上位机还负责FPGA任务的调度,即FPGA完成的计算任务都是在上位机的控制下完成的。

4.3 上位机调度流程上位机流程如图 9所示。FPGA调度由硬件模块精简控制,按照轻量化网络计算的一层一层完成,每一层的计算主要按照配置参数启动计算、完成计算。FPGA调度流程如图 10所示。

|

Download:

|

| 图 9 上位机流程 Fig. 9 Procedure of host computer | |

|

Download:

|

| 图 10 FPGA调度流程 Fig. 10 Procedure of FPGA scheduling | |

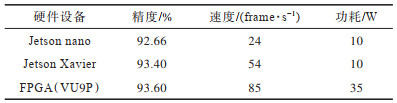

FPGA选择690T和VU9P 2种芯片作为实现芯片,其中690T是目前国产芯片能够达到最大容量的FPGA芯片,VU9P则具有更高的容量。本文选择2种嵌入式GPU作为参照,其中Jetson Xavier是英伟达最新的嵌入式GPU。

数据集采用sar图像数据集,网络结构选择轻量化网络结构Yolo tiny和MobileNetV3 & YoloV3。

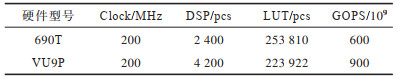

5.2 时钟频率与资源利用情况表 1给出了本文设计的处理器在两种芯片上的时钟频率和资源利用情况。由于本文采用参数化设计技术,设计的神经网络处理器可以根据FPGA的容量进行伸缩。在容量较少的芯片(690T)上,可以使用较少的硬件资源,速度也较慢。在容量加大的芯片(VU9P)上,使用较多的资源,从而达到更高的速度。

|

下载CSV 表 1 主频与资源利用情况 Table 1 Main frequency and resource utilization |

通过修改上位机程序,首先完成了Yolo Tiny网络在FPGA上的实现,Yolo Tiny结构没有使用DW和PW模块。表 2给出了Yolo Tiny在不同设备上的精度和性能,其中FPGA指的是VU9P。可以看出:尽管FPGA使用INT8格式,但其精度与嵌入式GPU相当;在速度上,FPGA能达到85 frame/s,超过了Jetson nano和Jetson Xavier;当然,FPGA开发板的功耗也是最高的,达到35 W。

|

下载CSV 表 2 Yolo Tiny在不同设备上的性能对比 Table 2 Yolo Tiny performance comparison in different devices |

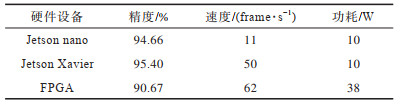

与Yolo Tiny结构不同,YoloV3 & MobileNetV3[20-21]是一种轻量化的网络结构,其中大量使用轻量化模块(DW和PW)。表 3给出了YoloV3 & MobileNetV3在不同设备上的精度和性能。可以看出:在精度上,FPGA实现精度下降约4%,这也是可以接受的精度损失;在速度上,FPGA实现能达到62 frame/s,同样超过Jetson nano和Jetson Xavier实现;相对于Yolo Tiny实现,YoloV3 & MobileNetV3的功耗从35 W提高到了38 W,这也是因为YoloV3 & MobileNetV3使用了DW和PW模块导致的。

|

下载CSV 表 3 YoloV3 & MobileNetV3在不同设备上的性能对比 Table 3 Performance comparison of YoloV3 & MobileNetV3 in different devices |

当FPGA加速器不包含轻量化模块时,实现YoloV3 & MobileNetV3模型的方法有2种,一种是使用Conv2d模块替代DW和PW(通过填零来实现),另一种是将中间结果传回主机,由主机的CPU实现DW模块和PW模块。

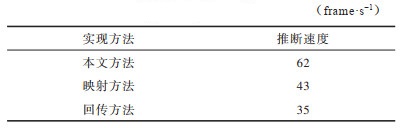

表 4给出了这2种实现方法与本文设计的对比,通过实验数据可知,使用轻量化模块的推断速度远比其他2种方法速度快。

|

下载CSV 表 4 轻量化模型性能对比 Table 4 Performance comparison of lightweight models |

为提高嵌入式GPU的运行速度和性能,本文设计并实现一种轻量化的神经网络加速器,通过优化实现PW、DW模块,在一定程度上满足低时延、低功耗的要求。同时该加速器支持指令执行,可以应用于不同的网络结构。实验结果表明,本文设计的神经网络加速器在VU9P FPGA芯片上可达到较快速度,并且功耗较低,可以完成受限平台中的目标检测任务。下一步将实现本文设计对4 bit、2 bit等更低比特精度量化的支持,并提高资源利用率,从而进一步优化加速器性能。

| [1] |

QIU J, WANG J, YAO S, et al. Going deeper with embedded FPGA platform for convolutional neural network[C]//Proceedings of 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. New York, USA: ACM Press, 2016: 26-35.

|

| [2] |

SHEN Y R, HAN T, YANG Q, et al. CS-CNN: enabling robust and efficient convolutional neural networks inference for Internet-of-things applications[J]. IEEE Access, 2018, 6: 13439-13448. DOI:10.1109/ACCESS.2018.2810264 |

| [3] |

ZHANG X Y, ZHOU X Y, LIN M X, et al. ShuffleNet: an extremely efficient convolutional neural network for mobile device[C]//Proceedings of 2018 IEEE Conference on Computer Vision and Pattern Recognition. Washington D.C., USA: IEEE Press, 2018: 6848-6856.

|

| [4] |

CUI X L, CHEN H Y, CUI X X, et al. A prototype of software and hardware collaborative design tool and its design description method[J]. Microelectronics and Computer, 2007, 24(6): 28-30. (in Chinese) 崔小乐, 陈红英, 崔小欣, 等. 一种软硬件协同设计工具原型及其设计描述方法[J]. 微电子学与计算机, 2007, 24(6): 28-30. |

| [5] |

ABDELOUAHAB K, BOURRASSET C, PELCAT M, et al. A holistic approach for optimizing DSP block utilization of a CNN implementation on FPGA[C]//Proceedings of the 10th International Conference on Distributed Smart Camera. Paris, France: [s. n. ], 2016: 69-75.

|

| [6] |

WU B C, IANDOLA F, JIN P H, et al. SqueezeDet: unified, small, low power fully convolutional neural networks for real-time object detection for autonomous driving[C]//Proceedings of 2017 IEEE Conference on Computer Vision and Pattern Recognition. Washington D.C., USA: IEEE Press, 2017: 446-454.

|

| [7] |

CHOLLET F. Xception: deep learning with depthwise separable convolutions[C]//Proceedings of 2017 IEEE Conference on Computer Vision and Pattern Recognition. Washington D.C., USA: IEEE Press, 2017: 1251-1258.

|

| [8] |

ZHANG C, SUN G, FANG Z, et al. Caffeine: towards uniformed representation and acceleration for deep convolutional neural networks[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 46(9): 2231-2321. |

| [9] |

DESOLI G, CHAWLA N, BOESCH T, et al. Deep convolutional neural network SoC in FD-SOI 28 nm for intelligent embedded systems[C]//Proceedings of 2017 Asian Solid-State Circuits Conference. Washington D.C., USA: IEEE Press, 2017: 1-5.

|

| [10] |

JACOB B, KLIGYS S, CHEN B, et al. Quantization and training of neural networks for efficient integer-arithmetic-only inference[C]//Proceedings of 2018 IEEE/CVF Conference on Computer Vision and Pattern Recognition. Washington D.C., USA: IEEE Press, 2018: 1-5.

|

| [11] |

KRISHNAMOORTHI R. Quantizing deep convolutional networks for efficient inference: a whitepaper[EB/OL]. [2020-05-20]. https://arxiv.org/pdf/1806.08342v1.pdf.

|

| [12] |

HU J, SHEN L, ALBANIE S, et al. Squeeze-and-excitation networks[J]. IEEE Transactions on Pattern Analysis and Machine Intelligence, 2020, 42(8): 2011-2023. DOI:10.1109/TPAMI.2019.2913372 |

| [13] |

PEEMEN M, SETIO A A A, MESMAN B, et al. Memory-centric accelerator design for convolutional neural networks[C]//Proceedings of the 10th International Conference on Distributed Smart Camera. Washington D.C., USA: IEEE Press, 2013: 1-5.

|

| [14] |

LU Z, CHEN Y, LI T, et al. Embedded FPGA convolutional neural network construction method for edge computing[J]. Computer Research and Development, 2018, 55(3): 551-562. (in Chinese) 卢冶, 陈瑶, 李涛, 等. 面向边缘计算的嵌入式FPGA卷积神经网络构建方法[J]. 计算机研究与发展, 2018, 55(3): 551-562. |

| [15] |

LI X Y, LIU F Y, WEN P C, et al. Convolutional neural network software and hardware coacceleration technology[J]. Aircraft Weapon, 2021, 28(3): 99-104. (in Chinese) 李欣瑶, 刘飞阳, 文鹏程, 等. 卷积神经网络的软硬件协同加速技术[J]. 航空兵器, 2021, 28(3): 99-104. |

| [16] |

SANKARADAS M, JAKKULA V, CADAMBI S, et al. A massively parallel coprocessor for convolutional neural networks[C]//Proceedings of the 20th IEEE International Conference on Application-Specific Systems, Architectures and Processors. Washington D.C., USA: IEEE Press, 2009: 53-60.

|

| [17] |

CADAMBI S, MAJUMDAR A, BECCHI M, et al. A programmable parallel accelerator for learning and classification[C]//Proceedings of the 19th International Conference on Parallel Architectures and Compilation Techniques. Vienna, Austria: [s. n. ], 2010: 273-284.

|

| [18] |

OVTCHAROV K, RUWASE O, KIM J Y, et al. Accelerating deep convolutional neural networks using specialized hardware[J]. Microsoft Research Whitepaper, 2015, 2(11): 11-14. |

| [19] |

MOTAMEDI M, GYSEL P, AKELLA V, et al. Design space exploration of FPGA-based deep convolutional neural networks[C]//Proceedings of the 21st Asia and South Pacific Design Automation Conference. Macao, China: [s. n. ], 2016: 575-580.

|

| [20] |

HOWARD A, SANDLER M, CHEN B, et al. Searching for MobileNetV3[C]//Proceedings of 2019 IEEE/CVF International Conference on Computer Vision. Washington D.C., USA: IEEE Press, 2020: 1-5.

|

| [21] |

REDMON J, FARHADI A. Yolov3: an incremental improvement[EB/OL]. [2020-05-20]. https://arxiv.org/pdf/1804.02767v1.pdf.

|

2021, Vol. 47

2021, Vol. 47